Mostrar el registro sencillo del ítem

dc.contributor.author

Lifschitz, Omar D.

dc.contributor.author

Rodriguez, Juan Agustin

dc.contributor.author

Julian, Pedro Marcelo

dc.contributor.author

Agamennoni, Osvaldo Enrique

dc.date.available

2020-04-14T19:28:20Z

dc.date.issued

2011-07

dc.identifier.citation

Lifschitz, Omar D.; Rodriguez, Juan Agustin; Julian, Pedro Marcelo; Agamennoni, Osvaldo Enrique; Post-silicon Validation Procedure for a PWL ASIC Microprocessor Architecture; Institute of Electrical and Electronics Engineers; IEEE Latin America Transactions; 9; 4; 7-2011; 492-497

dc.identifier.issn

1548-0992

dc.identifier.uri

http://hdl.handle.net/11336/102526

dc.description.abstract

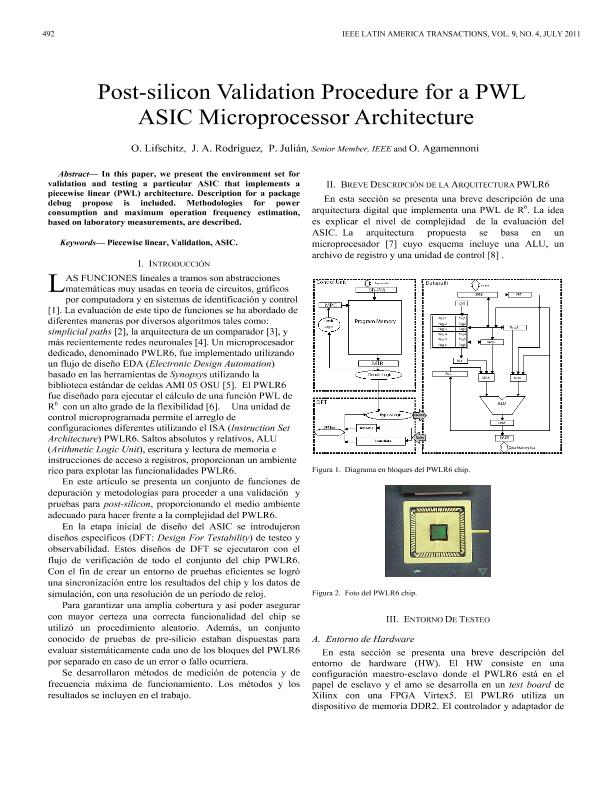

In this paper, we present the environment set for validation and testing a particular ASIC that implements a piecewise linear (PWL) architecture. Description for a package debug propose is included. Methodologies for power consumption and maximum operation frequency estimation, based on laboratory measurements, are described.

dc.format

application/pdf

dc.language.iso

eng

dc.publisher

Institute of Electrical and Electronics Engineers

dc.rights

info:eu-repo/semantics/openAccess

dc.rights.uri

https://creativecommons.org/licenses/by-nc-sa/2.5/ar/

dc.subject

Piece Wise Linear

dc.subject

ASIC

dc.subject

Nonlinear Systems

dc.subject.classification

Ingeniería Eléctrica y Electrónica

dc.subject.classification

Ingeniería Eléctrica, Ingeniería Electrónica e Ingeniería de la Información

dc.subject.classification

INGENIERÍAS Y TECNOLOGÍAS

dc.title

Post-silicon Validation Procedure for a PWL ASIC Microprocessor Architecture

dc.type

info:eu-repo/semantics/article

dc.type

info:ar-repo/semantics/artículo

dc.type

info:eu-repo/semantics/publishedVersion

dc.date.updated

2020-04-07T13:33:20Z

dc.journal.volume

9

dc.journal.number

4

dc.journal.pagination

492-497

dc.journal.pais

Estados Unidos

dc.journal.ciudad

Nueva Jersey

dc.description.fil

Fil: Lifschitz, Omar D.. Universidad Nacional del Sur; Argentina

dc.description.fil

Fil: Rodriguez, Juan Agustin. Consejo Nacional de Investigaciones Científicas y Técnicas. Centro Científico Tecnológico Conicet - Bahía Blanca. Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages". Universidad Nacional del Sur. Departamento de Ingeniería Eléctrica y de Computadoras. Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages"; Argentina

dc.description.fil

Fil: Julian, Pedro Marcelo. Consejo Nacional de Investigaciones Científicas y Técnicas. Centro Científico Tecnológico Conicet - Bahía Blanca. Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages". Universidad Nacional del Sur. Departamento de Ingeniería Eléctrica y de Computadoras. Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages"; Argentina

dc.description.fil

Fil: Agamennoni, Osvaldo Enrique. Universidad Nacional del Sur. Departamento de Ingeniería Eléctrica y de Computadoras; Argentina

dc.journal.title

IEEE Latin America Transactions

dc.relation.alternativeid

info:eu-repo/semantics/altIdentifier/url/https://ieeexplore.ieee.org/document/5993733

dc.relation.alternativeid

info:eu-repo/semantics/altIdentifier/doi/https://doi.org/10.1109/TLA.2011.5993733

Archivos asociados