Artículo

Post-silicon Validation Procedure for a PWL ASIC Microprocessor Architecture

Fecha de publicación:

07/2011

Editorial:

Institute of Electrical and Electronics Engineers

Revista:

IEEE Latin America Transactions

ISSN:

1548-0992

Idioma:

Inglés

Tipo de recurso:

Artículo publicado

Clasificación temática:

Resumen

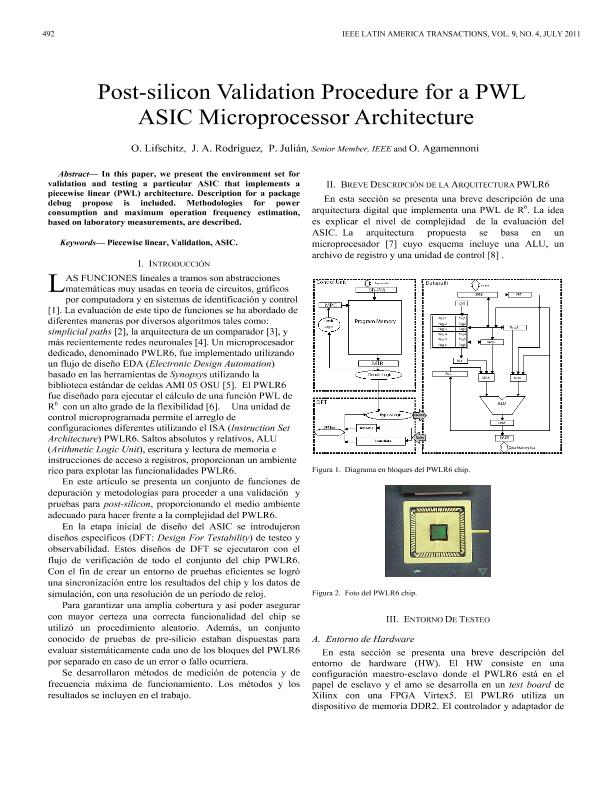

In this paper, we present the environment set for validation and testing a particular ASIC that implements a piecewise linear (PWL) architecture. Description for a package debug propose is included. Methodologies for power consumption and maximum operation frequency estimation, based on laboratory measurements, are described.

Palabras clave:

Piece Wise Linear

,

ASIC

,

Nonlinear Systems

Archivos asociados

Licencia

Identificadores

Colecciones

Articulos(IIIE)

Articulos de INST.DE INVEST.EN ING.ELECTRICA "A.DESAGES"

Articulos de INST.DE INVEST.EN ING.ELECTRICA "A.DESAGES"

Citación

Lifschitz, Omar D.; Rodriguez, Juan Agustin; Julian, Pedro Marcelo; Agamennoni, Osvaldo Enrique; Post-silicon Validation Procedure for a PWL ASIC Microprocessor Architecture; Institute of Electrical and Electronics Engineers; IEEE Latin America Transactions; 9; 4; 7-2011; 492-497

Compartir

Altmétricas