Mostrar el registro sencillo del ítem

dc.contributor.author

Reyes, Benjamín Tomás

dc.contributor.author

Sanchez, Raúl M.

dc.contributor.author

Pola, Ariel Luis

dc.contributor.author

Hueda, Mario Rafael

dc.date.available

2022-12-01T14:54:16Z

dc.date.issued

2016-12

dc.identifier.citation

Reyes, Benjamín Tomás; Sanchez, Raúl M.; Pola, Ariel Luis; Hueda, Mario Rafael; Design and Experimental Evaluation of a Time- Interleaved ADC Calibration Algorithm for Application in High-Speed Communication Systems; Institute of Electrical and Electronics Engineers; IEEE Transactions on Circuits and Systems I: Regular Papers; 64; 5; 12-2016; 1019-1030

dc.identifier.issn

1549-8328

dc.identifier.uri

http://hdl.handle.net/11336/179810

dc.description.abstract

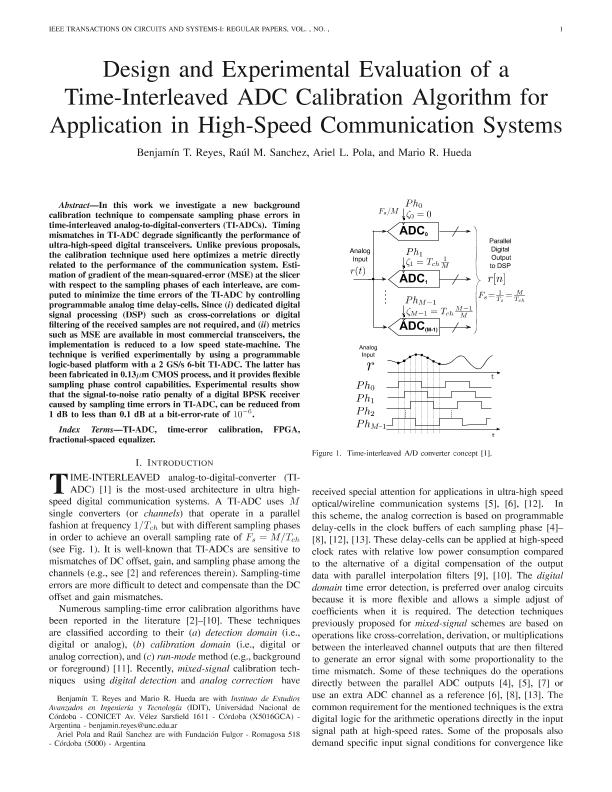

In this work we investigate a new background calibration technique to compensate sampling phase errors in time-interleaved analog-to-digital-converters (TI-ADCs). Timing mismatches in TI-ADC degrade significantly the performance of ultra-high-speed digital transceivers. Unlike previous proposals, the calibration technique used here optimizes a metric directly related to the performance of the communication system. Estimation of gradient of the mean-squared-error (MSE) at the slicer with respect to the sampling phases of each interleave, are computed to minimize the time errors of the TI-ADC by controlling programmable analog time delay-cells. Since (i) dedicated digital signal processing (DSP) such as cross-correlations or digital filtering of the received samples are not required, and (ii) metrics such as MSE are available in most commercial transceivers, the implementation is reduced to a low speed state-machine. The technique is verified experimentally by using a programmable logic-based platform with a 2 GS/s 6-bit TI-ADC. The latter has been fabricated in 0.13μm CMOS process, and it provides flexible sampling phase control capabilities. Experimental results show that the signal-to-noise ratio penalty of a digital BPSK receiver caused by sampling time errors in TI-ADC, can be reduced from 1 dB to less than 0.1 dB at a bit-error-rate of 10-6.

dc.format

application/pdf

dc.language.iso

eng

dc.publisher

Institute of Electrical and Electronics Engineers

dc.rights

info:eu-repo/semantics/openAccess

dc.rights.uri

https://creativecommons.org/licenses/by-nc-sa/2.5/ar/

dc.subject

FPGA

dc.subject

FRACTIONAL-SPACED EQUALIZER

dc.subject

TI-ADC

dc.subject

TIME-ERROR CALIBRATION

dc.subject.classification

Ingeniería de Sistemas y Comunicaciones

dc.subject.classification

Ingeniería Eléctrica, Ingeniería Electrónica e Ingeniería de la Información

dc.subject.classification

INGENIERÍAS Y TECNOLOGÍAS

dc.title

Design and Experimental Evaluation of a Time- Interleaved ADC Calibration Algorithm for Application in High-Speed Communication Systems

dc.type

info:eu-repo/semantics/article

dc.type

info:ar-repo/semantics/artículo

dc.type

info:eu-repo/semantics/publishedVersion

dc.date.updated

2022-12-01T14:22:07Z

dc.journal.volume

64

dc.journal.number

5

dc.journal.pagination

1019-1030

dc.journal.pais

Estados Unidos

dc.journal.ciudad

New York

dc.description.fil

Fil: Reyes, Benjamín Tomás. Consejo Nacional de Investigaciones Científicas y Técnicas. Centro Científico Tecnológico Conicet - Córdoba. Instituto de Estudios Avanzados en Ingeniería y Tecnología. Universidad Nacional de Córdoba. Facultad de Ciencias Exactas Físicas y Naturales. Instituto de Estudios Avanzados en Ingeniería y Tecnología; Argentina

dc.description.fil

Fil: Sanchez, Raúl M.. Fundación Fulgor; Argentina

dc.description.fil

Fil: Pola, Ariel Luis. Fundación Fulgor; Argentina

dc.description.fil

Fil: Hueda, Mario Rafael. Consejo Nacional de Investigaciones Científicas y Técnicas. Centro Científico Tecnológico Conicet - Córdoba. Instituto de Estudios Avanzados en Ingeniería y Tecnología. Universidad Nacional de Córdoba. Facultad de Ciencias Exactas Físicas y Naturales. Instituto de Estudios Avanzados en Ingeniería y Tecnología; Argentina

dc.journal.title

IEEE Transactions on Circuits and Systems I: Regular Papers

dc.relation.alternativeid

info:eu-repo/semantics/altIdentifier/url/https://doi.org/10.1109/TCSI.2016.2636209

dc.relation.alternativeid

info:eu-repo/semantics/altIdentifier/doi/http://dx.doi.org/10.1109/TCSI.2016.2636209

Archivos asociados