Mostrar el registro sencillo del ítem

dc.contributor.author

Villemur, Martin

dc.contributor.author

Julian, Pedro Marcelo

dc.contributor.author

Andreou, Andreas

dc.date.available

2019-10-18T19:58:59Z

dc.date.issued

2018-04

dc.identifier.citation

Villemur, Martin; Julian, Pedro Marcelo; Andreou, Andreas; Energy aware simplicial processor for embedded morphological visual processing in intelligent internet of things; Institution of Engineering and Technology; Electronics Letters; 54; 7; 4-2018; 420-422

dc.identifier.issn

0013-5194

dc.identifier.uri

http://hdl.handle.net/11336/86483

dc.description.abstract

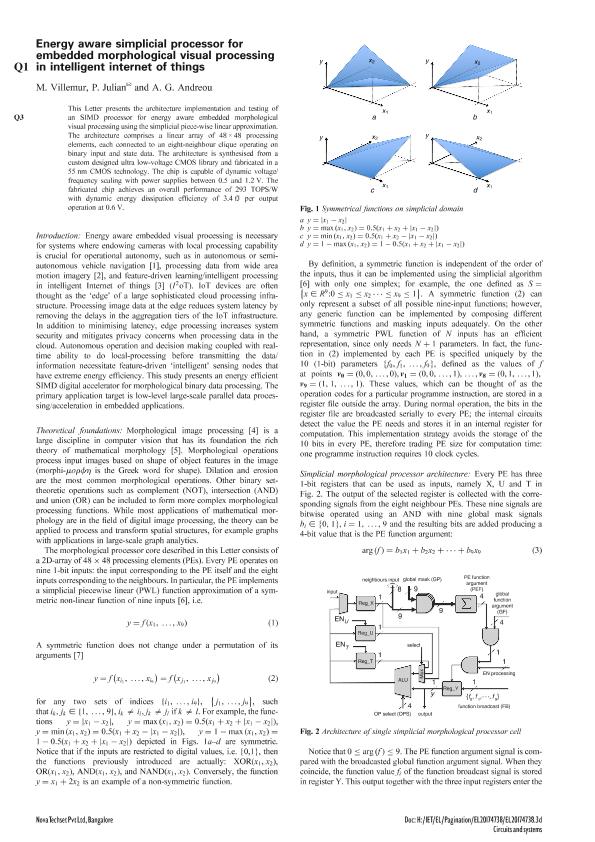

This Letter presents the architecture implementation and testing of an single instruction multiple data (SIMD) processor for energy aware embedded morphological visual processing using the simplicial piece-wise linear approximation. The architecture comprises a linear array of 48 × 48 processing elements, each connected to an eight-neighbour clique operating on binary input and state data. The architecture is synthesised from a custom designed ultra low-voltage CMOS library and fabricated in a 55 nm CMOS technology. The chip is capable of dynamic voltage/frequency scaling with power supplies between 0.5 and 1.2 V. The fabricated chip achieves an overall performance of 293 TOPS/W with dynamic energy dissipation efficiency of 3.4 fJ per output operation at 0.6 V.

dc.format

application/pdf

dc.language.iso

eng

dc.publisher

Institution of Engineering and Technology

dc.rights

info:eu-repo/semantics/openAccess

dc.rights.uri

https://creativecommons.org/licenses/by-nc-nd/2.5/ar/

dc.subject

VLSI

dc.subject

Internet of Things

dc.subject

Neural chips

dc.subject.classification

Ingeniería Eléctrica y Electrónica

dc.subject.classification

Ingeniería Eléctrica, Ingeniería Electrónica e Ingeniería de la Información

dc.subject.classification

INGENIERÍAS Y TECNOLOGÍAS

dc.title

Energy aware simplicial processor for embedded morphological visual processing in intelligent internet of things

dc.type

info:eu-repo/semantics/article

dc.type

info:ar-repo/semantics/artículo

dc.type

info:eu-repo/semantics/publishedVersion

dc.date.updated

2019-10-15T13:37:14Z

dc.journal.volume

54

dc.journal.number

7

dc.journal.pagination

420-422

dc.journal.pais

Reino Unido

dc.journal.ciudad

Londres

dc.description.fil

Fil: Villemur, Martin. Consejo Nacional de Investigaciones Científicas y Técnicas. Centro Científico Tecnológico Conicet - Bahía Blanca. Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages". Universidad Nacional del Sur. Departamento de Ingeniería Eléctrica y de Computadoras. Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages"; Argentina

dc.description.fil

Fil: Julian, Pedro Marcelo. Consejo Nacional de Investigaciones Científicas y Técnicas. Centro Científico Tecnológico Conicet - Bahía Blanca. Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages". Universidad Nacional del Sur. Departamento de Ingeniería Eléctrica y de Computadoras. Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages"; Argentina

dc.description.fil

Fil: Andreou, Andreas. University Johns Hopkins; Estados Unidos

dc.journal.title

Electronics Letters

dc.relation.alternativeid

info:eu-repo/semantics/altIdentifier/url/https://ieeexplore.ieee.org/document/8326382

dc.relation.alternativeid

info:eu-repo/semantics/altIdentifier/doi/http://dx.doi.org/10.1049/el.2017.4738

Archivos asociados