Phys. Status Solidi A, 1-5 (2014) / DOI 10.1002/pssa.201431409

## Cobalt phthalocyanine-based submicrometric field-effect transistors

Federico Golmar<sup>1,2,3</sup>, Pablo Stoliar<sup>1,3,4</sup>, Carlos Monton<sup>5</sup>, Ilya Valmianski<sup>5</sup>, Ivan K. Schuller<sup>5</sup>, Luis E. Hueso<sup>1,6</sup>, and Fèlix Casanova\*<sup>1,6</sup>

Received 4 June 2014, revised 23 September 2014, accepted 26 September 2014 Published online 24 October 2014

Keywords organic electronics, organic field effect transistors, phthalocyanines

We present performance characteristics of nanoscaled cobalt phthalocyanine (CoPc)-based organic field-effect transistors (OFETs) as a function of channel length. We found a channel length range which maximizes the field effect mobility in a trade-off between the decrease in the number of organic grain boundaries and the increase of the electrode-organic contact region. Further reduction of channel length is limited by fringe

currents, which lead to an increased off current and to a degradation of the sub-threshold slope. From this, we define an optimal channel length of  $280\,\mathrm{nm}$  to  $1\,\mu\mathrm{m}$  for applications in submicrometric CoPc-based OFETs. Our results are particularly relevant for the miniaturization of chemical sensing OFETs, where metal phthalocyanines have proven to be excellent candidates for the fabrication of the transistor channel.

© 2014 WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim

1 Introduction Metal phthalocyanines (MPc) have high chemical and thermal stability as well as interesting semiconducting properties, which make them excellent candidates for organic field effect transistors (OFETs) [1–6]. In addition, the strong charge transport dependence on the chemical environment makes them also good candidates for chemical sensing. However, in order for MPc devices to be technologically relevant, they need to be miniaturized below the micrometer scale [7, 8]. Indeed, in the current literature there is a wealth of results regarding the miniaturization of OFETs down to the 100-nm regime (see [9] and references therein). The interest in the field is notorious since downscaling MPc-based OFETs would allow for increased circuit density and switching speed [10], while at the same time would decrease the negative effects due to grain boundaries and defects [11–13].

OFET miniaturization is hampered by two important problems. First, transport in devices with small active areas (sub- $\mu$ m<sup>2</sup>) is often dominated by the contact resistance at the electrode/organic layer interface [14–16]. Second, shortening the active channel increases the longitudinal

electric field strength, which can lead to fringe currents [17–20]. To account for the fringing currents, corrections need to be applied in the determination of the field-effect mobility, the intrinsic channel conductivity, and the on/off ratio [21].

Here, we report on the fabrication of sub-\(\mu\m^2\) cobalt phthalocyanine (CoPc)-based OFETs and the study of their carrier transport properties as a function of channel length. We chose CoPc (Fig. 1a) for its interesting chemical sensing properties, including an outstanding capability for the detection of low-hazard organic peroxide stimulants used in explosives [22]. We find that, while both the electrode-organic interface and the grain boundaries influence the field-effect mobility, at the smallest channel lengths large longitudinal electric fields result in increased off-current and sub-threshold slope. This analysis reveals an optimal channel length range for sub-\mu m<sup>2</sup> CoPc-based OFETs. Our study of the electrical response of CoPc-based OFETs in the submicrometer channel length regime might play a fundamental role in the development of smaller sensors.

<sup>&</sup>lt;sup>1</sup> CIC nanoGUNE, 20018 Donostia – San Sebastian, Basque Country, Spain

<sup>&</sup>lt;sup>2</sup> I.N.T.I.-CONICET, Buenos Aires, Argentina

<sup>&</sup>lt;sup>3</sup> ECyT, Universidad Nacional de San Martín, Buenos Aires, Argentina

<sup>&</sup>lt;sup>4</sup> IMN, Université de Nantes, CNRS, 44322 Nantes, France

<sup>&</sup>lt;sup>5</sup> Physics Department and CAN, University of California-San Diego, La Jolla, CA 92093, USA

<sup>&</sup>lt;sup>6</sup> IKERBASQUE, Basque Foundation for Science, 48011 Bilbao, Basque Country, Spain

<sup>\*</sup>Corresponding author: e-mail f.casanova@nanogune.eu, Phone: +34 943 574012, Fax: +34 943 574001

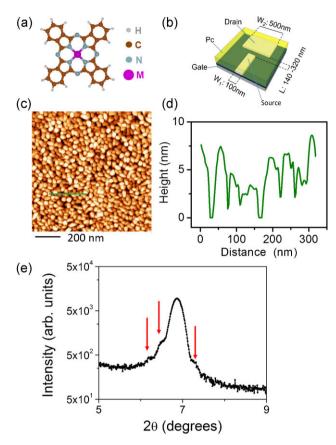

**Figure 1** (a) CoPc molecule. H, C, N, and M denotes hydrogen, carbon, nitrogen, and the metallic (Co) atom position, respectively. (b) Schematic nanometric OFET showing the nominal dimensions defined by e-beam lithography: channel length (L) and widths of the source ( $W_1$ ) and drain ( $W_2$ ) electrodes. (c) AFM height image of 40-nm-thick CoPc film deposited on SiO<sub>2</sub> substrate. (d) Height profile measured along the green line marked in (c). (e) XRD spectra of 40-nm-thick CoPc film deposited on SiO<sub>2</sub> substrate. The diffraction peak at 6.9° indicates that the CoPc plane forms approximately 65° with the substrate surface and stacks in a chevron structure. Finite size effect peaks (red arrows) indicate high degree of thickness uniformity.

**2 Experimental details** OFETs were prepared in the bottom-gate bottom-contacts configuration (Fig. 1b). All devices were fabricated on the same chip, consisting of a 150nm-thick SiO<sub>2</sub> thermally grown on a highly doped p<sup>++</sup>-type Si substrate. The Si substrate acts as a back gate electrode with the SiO<sub>2</sub> layer being the gate dielectric. Metal electrodes were fabricated using e-beam lithography followed by sputter deposition of 20 nm of Pd and lift-off. Channel lengths (L) were varied from 140 to 320 nm, while channel widths were kept constant for the drain ( $W_1 = 100 \,\mathrm{nm}$ ) and for the source ( $W_2 = 500 \text{ nm}$ ). The dimensions of the devices were checked by scanning electron microscopy. Different widths of the electrodes were used for making our transistors geometry as general as possible. In the same chip, we also fabricated a standard interdigitated transistor with  $L=1 \mu m$ as a reference for the submicrometric OFETs.

No gate primer or functionalization of the channel or the electrodes were used prior to the CoPc deposition. A 40-nmthick CoPc film was deposited in all devices on the chip by organic molecular beam deposition (OMBD) at a rate of  $0.5 \,\mathrm{\AA\,s^{-1}}$ , a base pressure of  $1.3 \times 10^{-10} \,\mathrm{mbar}$ , and a substrate temperature of 295 K. Film morphology was examined by atomic force microscopy (AFM) in a sample grown under the same conditions. We found that the film is polycrystalline (Fig. 1c and d) with a typical grain size of 50 nm and a root mean square roughness of 5 nm. X-ray diffraction (XRD) measurement (Fig. 1e) shows a peak at  $2\theta = 6.9^{\circ}$ , indicating that CoPc molecules are tilted 65° with respect to the substrate plane and are stacked in a chevron structure [23, 24]. The satellites about the central diffraction peak (red arrows) are finite size effects, and indicate a high degree of thickness uniformity [25].

Electrical measurements were performed in a LakeShore probe station under vacuum ( $10^{-5}$  mbar) and in darkness. A Keithley 4200 Semiconductor Characterization System with two source-measure units (SMU) with sub-femto-ampere preamplifiers was used to supply the gate voltage ( $V_{\rm GS}$ ) and the drain–source voltage ( $V_{\rm DS}$ ) while ( $I_{\rm DS}$ ) was being measured. The gate–source current ( $I_{\rm GS}$ ) was continuously monitored to ensure no significant gate leakage.

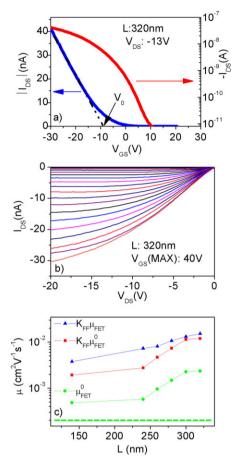

**3 Results and discussion** A typical transfer curve  $(I_{\rm DS}$  as a function of  $V_{\rm GS}$  for a given drain-source voltage,  $V_{\rm DS} = 13 \, \rm V$ ) is shown in Fig. 2a. The transfer curves are used to extract the field-effect mobility ( $k_{\text{FF}}\mu_{\text{FET}}$ , see below), the threshold voltage  $(V_{\rm th})$ , the on/off ratio  $(I_{\rm ON}/I_{\rm OFF})$ , and the subthreshold slope (S). However, the unconventional geometry of these devices requires particular procedures as discussed in Ref. [21]. The field-effect mobility is computed as  $k_{\text{FF}}\mu_{\text{FET}} = (L/W_1C_iV_{\text{DS}})(dI_{\text{DS}}/dV_{\text{GS}})$ , where  $dI_{DS}/dV_{GS}$  is the slope of the dashed line in Fig. 2a,  $C_i$ is the gate insulator capacitance per unit area, and  $k_{\rm FF}$ is a dimensionless form factor that takes into account geometry-specific fringe currents. Yet, the field effect mobility extracted in this way is not directly comparable with literature values because here we measure the transfer characteristics at much higher transverse electric field [21]. This further correction will be discussed below. The threshold voltage (Fig. 3a) is computed as  $V_{\rm th} = V_0 V_{\rm DS}/2$ , where  $V_0$  is the intercept of the dashed line in Fig. 2a [17]. The on/off ratio,  $I_{ON}/I_{OFF}$  (Fig. 3b), is calculated by taking  $I_{\rm OFF}$  to be the drain–source current at  $V_{\rm GS} = 10 \, \rm V$ , and  $I_{\rm ON}$  at  $V_{\rm GS} = -30 \, \rm V$ . The subthreshold slope (Fig. 3c) is  $S = [d(\log(I_{DS}))/dV_{GS}]^{-1}$ . All parameters obtained from the transfer characteristics correspond to the linear and subthreshold regimes.

Typical output characteristics ( $I_{\rm DS}$  as a function of  $V_{\rm DS}$  for different gate voltages) are shown in Fig. 2b. A clear saturation at high  $V_{\rm DS}$  confirms that the transistor is not operating in the short channel regime [26, 27]. The nonlinearity found at low  $V_{\rm DS}$  indicates the presence of injection problems due to the formation of a barrier at the electrode–organic interfaces [28].

Figure 2 (a) Transfer characteristics (i.e.,  $I_{\rm DS}$  as a function of  $V_{\rm GS}$ ) at a drain–source voltage  $V_{\rm DS}=-1\,\rm V$  for the device with  $L=320\,\rm nm$ .  $I_{\rm DS}$  is plotted both in a linear scale (blue line) and in a logarithmic scale (red line). The threshold voltage ( $V_{\rm th}$ ) and the uncorrected field-effect mobility ( $k_{\rm FF}\mu_{\rm FET}$ ) can be extracted from the former (dotted straight line), whereas the on-off ratio ( $I_{\rm ON}/I_{\rm OFF}$ ) and the subthreshold slope (S) can be obtained from the latter, as described in the text. (b) Output characteristics (i.e.,  $I_{\rm DS}$  as a function of  $V_{\rm DS}$ ) represented for different  $V_{\rm GS}$  from 0 to 40 V, in 2 V step, for the device with  $L=320\,\rm nm$ . (c) Zero-field mobility ( $\mu_{\rm FET}^0$ ) as a function of the OFET channel length. For comparison, the uncorrected field-effect mobility ( $k_{\rm FF}\mu_{\rm FET}$ ) at  $V_{\rm DS}=-5\,\rm V$  and the uncorrected zero-field mobility ( $k_{\rm FF}\mu_{\rm FET}^0$ ) are also plotted. The value obtained from interdigitated transistors with  $L=1\,\mu \rm m$  is indicated by the dashed line.

Dependence of  $k_{\rm FF}\mu_{\rm FET}$ ,  $k_{\rm FF}\mu_{\rm FET}^0$ , and the zero-field mobility ( $\mu_{\rm FET}^0$ ) on L are shown in Fig. 2c.  $k_{\rm FF}\mu_{\rm FET}^0$  is computed from  $k_{\rm FF}\mu_{\rm FET}$  using the Frenkel–Poole equation  $k_{\rm FF}\mu_{\rm FET}^0=k_{\rm FF}\mu_{\rm FET}\exp(-\beta\sqrt{V_{\rm DS}}/L)$ , where  $\beta$  is the temperature-corrected field-dependent coefficient. The actual zero-field mobility ( $\mu_{\rm FET}^0$ ) is then extracted from  $k_{\rm FF}\mu_{\rm FET}^0$  by computing the value of  $k_{\rm FF}$  for the specific device geometry [21]. The so corrected  $\mu_{\rm FET}^0$  values can be now compared with literature values for standard OFETs.

The zero-field mobility peaks for channel length  $L=320\,\mathrm{nm}$  at  $\mu_{\mathrm{FET}}^0\sim 10^{-3}\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$  (Fig. 2c). For

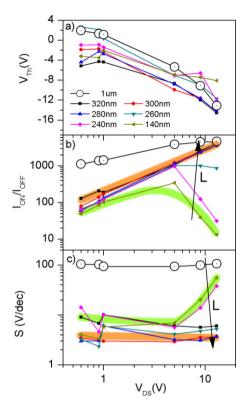

**Figure 3** (a) Threshold voltage, (b) on/off ratio, and (c) subthreshold slope measured as a function  $V_{\rm DS}$  and plotted in a logarithmic scale, for OFETs with different channel lengths L. Two different regimes depending on the channel length and  $V_{\rm DS}$  value in the on/off ratio and the sub-threshold slope are highlighted with continuous (green or orange) stripes as a guide to the eye. For comparison, the values obtained from an interdigitated transistor with  $L=1~\mu{\rm m}$  are shown with open circles.

longer channels (interdigitated geometry,  $L=1~\mu m$ , shown as a dashed line in Fig. 2c), the obtained value is  $\mu_{\rm FET}^0 \sim 2 \times 10^{-4}~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$ , which is in agreement with literature values for CoPc [29]. The lower  $\mu_{\rm FET}^0$  in longer channels is due to an increase in grain boundaries, which limits the charge transport in polycrystalline thin films [30].  $\mu_{\rm FET}^0$  also decreases for very short channels  $(5 \times 10^{-4}~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$  for  $L=140~{\rm nm}$ ), because the contact resistance becomes larger than the channel resistance when the channel length is comparable to (or smaller than) the size of the contact region [14, 31]. A similar trade-off between the negative effect of grain boundaries and the relative contact resistance has been observed in pentacene-based OFETs [21].

The dependence of  $V_{\rm th}$ ,  $I_{\rm ON}/I_{\rm OFF}$  ratio and S on  $V_{\rm DS}$  and L is summarized in Fig. 3. Reference data obtained for the interdigitated transistor is also included for comparison. Figure 3a shows  $V_{\rm th}$  as a function of  $V_{\rm DS}$  for different L devices. In an ideal transistor,  $V_{\rm th}$  should not change with L or  $V_{\rm DS}$  [32]. However, in these devices,  $V_{\rm th}$  decreases with increasing  $V_{\rm DS}$ . This behavior is known as "bias stress". This stress due to  $V_{\rm GS}$  bias is induced by the measurement sequence since every increase in  $V_{\rm DS}$  in the plot was

performed after a complete  $V_{\rm GS}$  sweep [33]. Indeed, bias stress manifests as a continuous shift of  $V_{\rm th}$  upon prolonged or repetitive application of gate bias [34]. On the other hand, the dispersion of  $V_{\rm th}$  for different L for a fixed  $V_{\rm DS}$  indicates the presence of trapped charges in the gate–dielectric interface [35].

Figure 3b shows the  $I_{ON}/I_{OFF}$  ratio as a function of  $V_{DS}$ for different L. As mentioned, it is computed as the ratio between the  $I_{DS}$  at  $V_{GS} = -30 \text{ V}$  and the  $I_{DS}$  at  $V_{GS} = 10 \text{ V}$ . Figure 2a shows that outside those values  $I_{DS}$  does not change significantly, but might produce a breakdown of the gate dielectrics. This measurement is limited by the noise level of the source-meter  $(10^{-11} \,\mathrm{A})$ , which determines the cut-off for the off state. Above 280 nm, the  $I_{\rm ON}/I_{\rm OFF}$  ratio increases linearly with  $V_{\rm DS}$ . This is because the measured  $I_{\rm OFF}$  value is limited by the source-meter resolution while the I<sub>ON</sub> value increases linearly with channel bias. Although in an ideal case the  $I_{ON}/I_{OFF}$  ratio is not expected to vary with L [36], a clear decrease in the on/off ratio appears for small  $L \leq 260 \,\mathrm{nm}$  above 5 V. This reduction is caused by the increase of the  $I_{OFF}$  value (above  $10^{-11}$  A) due to a parallel ohmic current flowing through the bulk of the CoPc channel that becomes relevant at a large enough longitudinal electric field (associated with a high  $V_{DS}$  and a small L) [36].

Sub-threshold slope S as a function of  $V_{DS}$  at different Lis presented on Fig. 3c. This parameter is not expected to vary with either  $V_{DS}$  or L [37]. For L > 250 nm, the observed variation of S with L is due to the device-to-device trap density variation at the interface of the gate-dielectric layer [38]. This further confirms uncontrolled presence of trapped charges at the gate dielectric interface. However, for the smallest channels ( $L \le 240 \,\mathrm{nm}$ ) and the highest applied fields  $(V_{DS} \ge 5 \text{ V})$  there is an increase in S indicating a clear degradation of the transistor performance. This behavior is related to the degradation observed in Fig. 3b caused by parallel ohmic currents, which results in a shift in the drain current and, consequently, the appearance of a long tail in the semi-log plot at the subthreshold region. Such an effect would lead to a more gradual onset of conduction, which would mainly affect transistor parameters extracted from the off regime (the  $I_{\rm ON}/I_{\rm OFF}$  ratio and S) and not from the on regime ( $\mu_{\text{FET}}^0$  and  $V_{\text{th}}$ ).

Finally, an optimal operational region for the performance of these devices can be defined based on the combination of all of the aforementioned effects. As a general rule, for transistors operating in the linear regime, it is useful to operate them at the maximum available  $V_{\rm DS}$  and the smallest possible L. As evident from Fig. 3, there is a trade-off between reduction of L below 260 nm and an increase in the absolute value of  $V_{\rm DS}$  above 5 V. This is an important limiting factor in the future use of MPc-based OFETs in applications where a high-density array of devices or high-operating voltages are needed. However, the results hold promise for OFET sensing applications where restrictions on channel lengths are not as stringent. At present it is not clear whether the deviations from ideality are related to the thin film growth or lithography and

therefore further studies of nanopatterned arrays of sensors is needed [1–3].

**4 Conclusions** In conclusion, we have studied the behavior of nanoscaled OFETs based on CoPc. We observe a clear improvement in the transport properties (field-effect mobility) with respect to their micrometer-sized counterparts. This is attributed to a decrease in the number of grain boundaries between electrodes. However, when the channel length is decreased below 320 nm and the length becomes comparable to (or smaller than) the extension of the contact region, the field-effect mobility decreases. This behavior is attributed to the contact resistance, which dominates the device transport at the smallest channel lengths. In addition, the large longitudinal electric fields at the smallest channel lengths cause fringing currents, which lead to an increased off current and to the degradation of the sub-threshold slope. These limitations define an optimal channel length of 280 nm to 1 µm for the applications of submicrometric CoPc-based OFETs, including chemical vapor sensing.

Acknowledgements This is a highly collaborative research. The experiments were conceived jointly, the data was extensively debated and the paper was written by multiple iterations between all the coauthors. Nanofabrication of the Pd electrodes and electronic measurements were done at CIC nanoGUNE. CoPc films were fabricated and characterized at UCSD (CM, IV and IKS). The work at CIC nanoGUNE was supported by the European Union 7<sup>th</sup> Framework Programme under the Marie Curie Actions (256470-ITAMOSCINOM) and the European Research Council (Grant 257654-SPINTROS), by the Spanish Ministry of Economy (Project No. MAT2012-37638 and Ramon y Cajal Program RYC-2012-01031), and by the Basque Government (Project No. PI2011-1). The research at UCSD was supported by the Office of Basic Energy Science, U.S. Department of Energy, BES-DMS funded by the Department of Energy's Office of Basic Energy Science, DMR under grant DE FG03 87ER-45332.

## References

- [1] J. E. Royer, J. Park, C. Colesniuc, J. S. Lee, T. Gredig, S. Lee, S. Jin, I. K. Schuller, W. C. Trogler, and A. C. Kummel, J. Vac. Sci. Technol. B 28, C5F22 (2010).

- [2] J. Park, J. E. Royer, C. N. Colesniuc, F. I. Bohrer, A. Sharoni, S. H. Jin, I. K. Schuller, W. C. Trogler, and A. C. Kummel, J. Appl. Phys. 106, 034505 (2009).

- [3] R. D. Yang, J. Park, C. N. Colesniuc, I. K. Schuller, J. E. Royer, W. C. Trogler, and A. C. Kummel, J. Chem. Phys. 130, 164703 (2009).

- [4] J. E. Royer, C. Y. Zhang, A. C. Kummel, and W. C. Trogler, Langmuir 28, 6192 (2012).

- [5] J. E. Royer, S. Lee, C. Chen, B. Ahn, W. C. Trogler, J. Kanicki, and A. C. Kummel, Sens. Actuators B 158, 333 (2011).

- [6] Y. Zhang, X. Cai, Y. Bian, and J. Jiang, in: Structure and Bonding, Vol. 135, edited by D. M. P. Mingos and J. Jiang (Springer, New York, 2010), pp. 275–322.

- [7] E. Cantatore, T. C. T. Geuns, G. H. Gelinck, E. van Veenendaal, A. F. A. Gruijthuijsen, L. Schrijnemakers, S. Drews, and D. M. de Leeuw, IEEE J. Solid-State Circuits 42, 84 (2007).

- [8] E. C. P. Smits, S. G. J. Mathijssen, P. A. van Hal, S. Setayesh, T. C. T. Geuns, K. A. H. A. Mutsaers, E. Cantatore, H. J. Wondergem, O. Werzer, R. Resel, M. Kemerink, S. Kirchmeyer, A. M. Muzafarov, S. A. Ponomarenko, B. de Boer, P. W. M. Blom, and D. M. de Leeuw, Nature 455, 956 (2008).

- [9] Y. Cao, M. L. Steigerwald, C. Nuckolls, and X. Guo, Adv. Mater. 22, 20 (2010).

- [10] M. Kitamura and Y. Arakawa, J. Phys.: Condens. Matter 20, 184011 (2008).

- [11] S. Verlaak and P. Heremans, Phys. Rev. B 75, 115127 (2007).

- [12] G. S. Tulevski, C. Nuckolls, A. Afzali, T. O. Graham, and C. R. Kagan, Appl. Phys. Lett. 89, 183101 (2006).

- [13] M. Tello, M. Chiesa, C. M. Duffy, and H. Sirringhaus, Adv. Funct. Mater. 18, 3907 (2008).

- [14] P. Stoliar, R. Kshirsagar, M. Massi, P. Annibale, C. Albonetti, D. M. de Leeuw, and F. Biscarini, J. Am. Chem. Soc. 129, 6477 (2007).

- [15] L. Burgi, T. J. Richards, R. H. Friend, and H. Sirringhaus, J. Appl. Phys. 94, 6129 (2003).

- [16] R. Joseph Kline, M. D. McGehee, and M. F. Toney, Nature Mater. 5, 222 (2006).

- [17] L. Wang, D. Fine, D. Basu, and A. Dodabalapur, J. Appl. Phys. 101, 054515 (2007).

- [18] F. Golmar, M. Gobbi, R. Llopis, P. Stoliar, F. Casanova, and L. E. Hueso, Org. Electron. 13, 2301 (2012).

- [19] L. Wang, D. Fine, T. Jung, D. Basu, H. von Seggern, and A. Dodabalapur, Appl. Phys. Lett. 85, 1772 (2004).

- [20] B. A. Mattis, Y. Pei, and V. Subramanian, Appl. Phys. Lett. 86, 033113 (2005).

- [21] F. Golmar, P. Stoliar, M. Gobbi, F. Casanova, and L. E. Hueso, Appl. Phys. Lett. 102, 103301 (2013).

- [22] J. E. Royer, E. D. Kappe, C. Zhang, D. T. Martin, W. C. Trogler, and A. C. Kummel, J. Phys. Chem. C 116(46), 24566 (2012).

- [23] C. Monton, I. Valmiansky, and I. K. Schuller, Appl. Phys. Lett. 101, 133304 (2012).

- [24] G. Liu, T. Gredig, and I. K. Schuller, EPL 83, 56001 (2008).

- [25] C. W. Miller, A. Sharoni, G. Liu, C. N. Colesniuc, B. Fruhberger, and I. K. Schuller, Phys. Rev. B 72, 104113 (2005).

- [26] S. M. Sze and K. K. Ng, Physics of Semiconductor Devices (John Wiley & Sons, Hoboken, New Jersey, 2007).

- [27] J. N. Haddock, X. Zhang, S. Zheng, Q. Zhang, S. R. Marder, and B. Kippelen, Org. Electron. 7, 45 (2006).

- [28] A. Kahn, N. Koch, and W. Gao, J. Polym. Sci. B, Polym. Phys. 41, 2529 (2003).

- [29] R. D. Yang, T. Gredig, C. N. Colesniuc, J. Park, I. K. Schuller, W. C. Trogler, and A. C. Kummel, Appl. Phys. Lett. 90, 263506 (2007).

- [30] P. Annibale, C. Albonetti, P. Stoliar, and F. Biscarini, J. Phys. Chem. A 111, 12854 (2007).

- [31] The extension of contact region we refer here is in the same axes of L and is independent of  $W_1$  and  $W_2$ . It depends on the interaction of the organic molecules with the electrodes and is expected to be, at maximum, few micrometers long.

- [32] H. Sakai, K. Konno, and H. Murata, Appl. Phys. Lett. 94, 073304 (2009).

- [33] S. G. J. Mathijssen, M. Cölle, A. J. G. Mank, M. Kemerink, P. A. Bobbert, and D. M. de Leeuw, Appl. Phys. Lett. 90, 192104 (2007).

- [34] P. D'Angelo, P. Stoliar, T. Cramer, A. Cassinese, F. Zerbetto, and F. Biscarini, Appl. Phys. A 95, 55 (2009).

- [35] G. Horowitz, R. Hajlaoui, H. Bouchriha, R. Bourguiga, and M. Hajlaoui, Adv. Mater. 10, 923 (1998).

- [36] A. R. Brown, C. P. Jarrett, D. M. de Leeuw, and M. Matters, Synth. Met. 88, 37 (1997).

- [37] H. Klauk, Chem. Soc. Rev. 39, 2643 (2010).

- [38] S. Scheinert, G. Paasch, M. Schrödner, H.-K. Roth, S. Sensfuß, and Th. Doll, J. Appl. Phys. 92, 330 (2002).