J. Inf. Commun. Converg. Eng. 22(2): 89-97, Jun. 2024

Regular paper

# Harnessing Integration of Symbol-Rate Equalizer and Timing Recovery for Enhanced Stability

Adrián Francisco Ramírez\* , Felipe Pasquevich, and Graciela Corral Briones

Digital Communications Laboratory, Faculty of Exact, Physical and Natural Sciences, National University of Córdoba, Vélez Sarsfield Avenue 1611, Córdoba, Argentina

## **Abstract**

This research conducted a comparative analysis of two communication systems. The first system utilizes a conventional series configuration consisting of a symbol-rate least mean square (LMS) equalizer followed by a timing recovery loop. The second system introduces an innovative approach that integrates a symbol-rate LMS equalizer and a timing recovery component within a single loop, allowing mutual feedback between the two blocks. In this integrated system, the equalizer also provides timing error information, thereby eliminating the requirement for a separate threshold error detector. This study examines the performance curves of both system configurations. The simulation results revealed that the integrated system may offer improved stability in terms of multiple transmission challenges, including phase and frequency offsets and intersymbol interference. Further analysis and discussion highlight the significant insights and implications of the proposed architecture. Overall, the present findings provide an alternative perspective on the joint implementation of equalization and timing recovery in communication systems.

Index Terms: Series system, Joint system, Timing recovery, Symbol-rate

# I. INTRODUCTION

Accomplishing stable signals is essential for effective transmission; however, challenges such as noise, dispersion, and reception inaccuracies emerge from channel impairments. Techniques such as equalization and timing recovery are imperative to mitigate these impairments and ensure accurate signal reception. In general, systems employ separate blocks for these techniques. The equalizer modifies filter coefficients to offset channel noise and intersymbol interference (ISI), whereas the timing recovery loop adjusts timing indices to address subpar temporal synchronization.

Gardner [1] introduces a threshold error detector (TED) that utilizes two samples per symbol obtained from a single signal to calculate the timing error. The comprehensive tim-

ing recovery system employing this block [2]. Subsequent work by Gardner [3] examines the curves of temporal error, filtered error, and the output of the numerically controlled oscillator (NCO), addressing both phase and frequency errors, within a system operating at 16 samples per symbol. Zhou [4] evaluated two configurations using this timing recovery loop: one with a series system including clock recovery and a feed-forward equalizer (FFE), and another that combines these blocks into a joint system. Zhou's study demonstrated that the joint system outperforms the series system under specific dispersion conditions, and could effectively manage the large frequency errors by processing the signal at a rate of two samples per symbol.

To date, several studies have explored enhancements and integrations of synchronization and equalization techniques

Received 5 November 2023, Revised 16 March 2024, Accepted 29 March 2024

\*Corresponding Author Adrián Francisco Ramírez (E-mail: adrian.ramirez@mi.unc.edu.ar)

Digital Comm. Lab., Faculty of Exact, Physical and Natural Sciences, National University of Córdoba, Vélez Sarsfield Av. 1611, Córdoba, Argentina

Open Access https://doi.org/10.56977/jicce.2024.22.2.89

print ISSN: 2234-8255 online ISSN: 2234-8883

©This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Copyright © The Korea Institute of Information and Communication Engineering

from various perspectives. Ref. [5] introduces an improved Gardner synchronization loop that incorporates Lagrangian cubic interpolation, which enhances synchronization performance by implementing a polarity selection mechanism prior to the timing error detector (TED) block. Ref. [6] proposes a timing recovery criterion that utilizes adaptive coefficients from a decision feedback equalizer (DFE) for digital subscriber line (DSL) systems, with adjustments modifying the sampling phase accordingly. Ref. [7] presents a convergence analysis of timing and carrier recovery loops employing an adaptive equalizer for digital communication channels, which emphasizes the critical selection of convergence parameters to prevent biases in time or carrier phase.

Ref. [8] describes an algorithm for symbol-rate timing recovery in DSL, and proposed a semi-analytical framework to determine the relationship between the variance of the time estimate, acceptable noise levels, and dead zone thresholds. Ref. [9] introduces a method for joint fractionallyspaced equalization and timing recovery, eliminating the need for separate circuits by utilizing the center of mass displacement of the equalizer weights for clock synchronization. Ref. [10] details an analog timing recovery implementation for a noise-predictive DFE, which results in faster operation and a significant reduction in jitter. Ref. [11] analyzes time jitter immunity using a phase detector based on the stochastic gradient algorithm and compares it with a method based on specific signal paths, all within the context of multi-level decision feedback equalization with clock recovery for magnetic recording channels.

Furthermore, Ref. [12] provides practical solutions for blind fractionally spaced equalization and timing synchronization in wireless fading channels. Finally, Ref. [13] proposes a joint carrier recovery and blind DFE for fast timevarying channels. Overall, although these articles present innovative ideas on related topics, they pose limitations such as inadequate cross-model comparisons, highly specialized algorithms, or the requirement for high-performance equalizers

Herein, we introduce a novel approach by integrating a symbol-rate LMS equalizer with a Gardner timing recovery mechanism into a unified closed-loop system. The key innovation of this system is the restoration of the time interval through error estimation, which is achieved by comparing the coefficients adjacent to the central coefficient of the symbol-rate equalizer. This method eliminates the need for a separate TED block. Such integration facilitates a more direct and dynamic interaction between the components, potentially improving the system stability.

The remainder of the paper is organized as follows: the series and joint system architectures along with the simulation setup and analysis scenarios are detailed in Section II. The performance curves obtained from various simulations are presented in Section III, providing insights under differ-

ent conditions. Finally, in Section IV, a comprehensive analysis of the results is presented along with conclusions and suggestions for future research directions.

#### II. SYSTEM MODELS AND METHODS

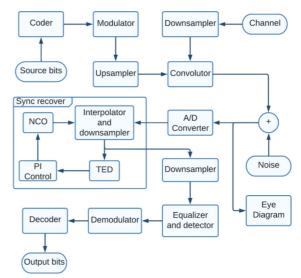

# A. Series system

The series system architecture, illustrated in Fig. 1, initiates by generating a random bitstream, encoding it into binary format, and modulating it into complex symbols using a predefined alphabet. The signal is then upsampled by a specific factor, resulting in a rate higher than the Nyquist rate. Subsequently, the channel is downsampled to align with the signal rate during convolution. Additive white Gaussian noise (AWGN) may also be introduced to the convolved signal. The process concludes with the signal undergoing analog-to-digital (A/D) conversion, which includes interpolation and resampling.

$Fig.\ 1.$  Series system scheme.

The synchronization loop adjusts the sampling time to correct any phase or frequency deviations in the received signal. It employs a NCO to determine the integer and fractional indices for mathematical interpolation. The interpolator then performs cubic Lagrange interpolation, aligning the samples to their correct positions and downsampling the signal.

A TED measures the error between consecutive symbols, which is proportional to phase and frequency discrepancies. The TED error is expressed in Equation 1, where e[n] represents the error at the n-th symbol, with  $s_I$  and  $s_Q$  denoting the in-phase and quadrature signals, respectively.

$$e[n] = 0.5(s_{I}[n-1/2](sign(s_{I}[n]) - sign(s_{I}[n-1])) + (1)$$

$$s_{O}[n-1/2](sign(s_{O}[n]) - sign(s_{O}[n-1])))$$

A proportional-integral (PI) controller calculates the input signal for the NCO based on the detected errors. The NCO contains a register that holds a fractional value representing the current phase of the oscillator, which fluctuates with each clock cycle. When this value exceeds zero, the register overflows and generates a new interpolation. The fractional value at this moment is used to calculate the fractional sampling interval.

Following the timing recovery loop, an additional downsampling operation is performed. The downsampling block also determines the initial sample of the potential downsampled signals by measuring the distance of the samples from the constellation symbols.

Subsequently, the equalization process occurs. A symbolrate LMS equalizer is employed, and its complex weights are continuously adapted to minimize the error between the received symbols and the expected values. By optimizing the filter coefficients, the equalizer can more effectively compensate for the channel impairments, and thus, improve the signal quality.

After equalization, the symbols are detected by comparing the Euclidean distance between the equalized symbols and each symbol in the alphabet. The symbol corresponding to the smallest distance is selected in each case. These symbols are then demodulated and converted back into their original format. Subsequently, the recovered symbols are decoded to retrieve the transmitted bits. The decoding process thus converts the sequence of demodulated symbols into a binary bit-stream, reproducing the information originally transmitted by the source.

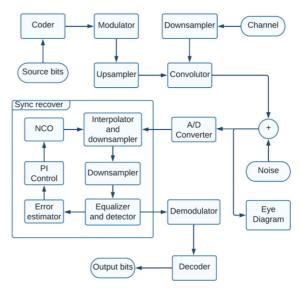

### B. Joint system

As depicted in Fig. 2, the joint system shares common functions with the series system, which establishes a basis for generating, processing, and converting the transmitted signal. These shared functions ensure consistency and compatibility between the two systems, while also enabling the joint communication system to perform unique operations beyond the common steps.

Initially, the system generates a random bitstream, encodes and modulates it into complex symbols, performs upsampling, processes the signal through the communication channel, and undergoes A/D conversion. Subsequently, it diverges from the previous scheme. Finally, as in the series architecture, the symbols are demodulated and decoded to recover the transmitted binary information.

The joint system integrates the stages of symbol equalization, detection, and timing recovery into a unified loop. Sim-

Fig. 2. Joint system scheme.

ilar to the series system, this system utilizes a symbol-rate LMS equalizer for symbol equalization. This equalizer iteratively adapts its filter coefficients to counteract distortions caused by the channel, thereby reducing the ISI. The detection is conducted by comparing each symbol to the constellation points.

Both the PI controller and the NCO are implemented as in the series system. However, the timing error is estimated by subtracting the values of the two coefficients adjacent to the central coefficient, thereby eliminating the need for a traditional TED in the timing recovery stage. The error formula is presented in Equation 2, where e[n] represents the error at the n-th symbol, N denotes the number of equalizer coefficients, and taps refers to the vector of coefficients, which are updated at each symbol interval.

$$e[n] = taps[floor(N/2) + 1] - taps[floor(N/2) - 1]$$

(2)

This scheme posits that the timing recovery, by leveraging the error information from the equalizer coefficients, enhances synchronization accuracy. Improved synchronization, in turn, improves the performance of the equalizer by providing a more synchronized and better-shaped signal.

## C. Simulation setup

In all experiments, the number of randomly generated symbols transmitted is fixed at 1000. Quadrature amplitude modulation is employed for transmitting information. The channel model utilizes a raised cosine function with a roll-off factor of 0.7. The detection of received symbols incurs a phase error equivalent to the duration of a quarter of a sym-

bol. Each equalizer comprises seven coefficients, and employs a variable step size, starting at 0.1 and reducing by half every third of the total symbols. The simulations are conducted in the absence of AWGN.

Moreover, in both systems, the upsampling rate is set to four, allowing the timing recovery to process a signal consisting of four samples per symbol. The signals input to the equalization and detection blocks are at symbol rate, following prior downsampling stages.

Table 1 outlines the simulation setup, detailing various scenarios labeled as Scenario 1, Scenario 2, and so forth, up to six scenarios. These scenarios are designed to assess the impact of ISI, which may be absent, low, or high, and the effect of frequency deviation, which may be zero or a specific value. The conditions in each scenario reflect potential adverse conditions in the channel model and during symbol detection.

Table 1. Simulation setup

| Parameters       | Scenario specific values |       |       |       |       |       |

|------------------|--------------------------|-------|-------|-------|-------|-------|

|                  | Sc. 1                    | Sc. 2 | Sc. 3 | Sc. 4 | Sc. 5 | Sc. 6 |

| Frequency offset | 0                        | 0.001 | 0     | 0.001 | 0     | 0.001 |

| ISI level        | 0                        | 0     | 0.05  | 0.05  | 0.15  | 0.15  |

Specifically, the "Frequency offset" parameter indicates the frequency deviation during symbol detection. Scenarios 2, 4, and 6 include a frequency offset of 0.001, equivalent to 0.1% of the ideal symbol time, whereas the remaining scenarios include no frequency offset. Conversely, the "ISI level" parameter measures the amount of ISI relative to the ideal channel. This is modeled by assuming a Gaussian distribution function with zero mean and a variance equal to the ISI level. A single random sample from this distribution generates a set of values representing a deterministic interference signal, which is then superimposed on the ideal raised cosine channel to create a channel model with ISI.

# III. RESULTS

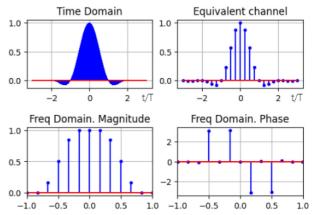

### A. Non-ISI channel

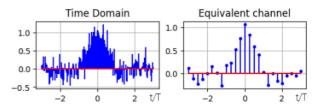

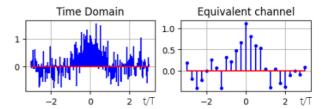

This case pertains to scenarios 1 and 2, where no ISI affects the channel. Fig. 3 illustrates the channel model in the time domain, presenting both continuous-time and discrete-time representations (where "t" denotes time and "T" represents the interval at which symbol pulses are uniformly spaced). The discrete-time equivalent channel has a sampling rate of four samples per symbol. Below these representations, the graphs depict the frequency response of the channel in terms of magnitude and phase.

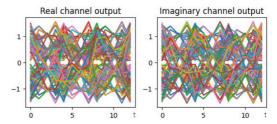

Fig. 4 displays the eye diagram of the signal input to the A/D converter. This diagram clearly shows two distinct images, representing the real and imaginary components of the signal. The eye diagram features well-defined open eyes, indicating that all potential symbol transitions are precisely aligned at each symbol interval.

${\bf Fig.~3.}$  Channel for scenarios 1 and 2: time domain, equivalent model, magnitude and phase.

Fig. 4. Eye diagram for scenarios 1 and 2.

### 1) Scenario 1. Series system:

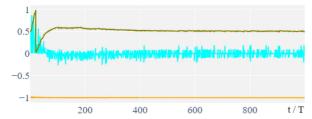

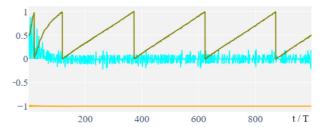

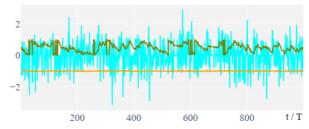

Fig. 5 presents the timing recovery curves. The light blue curve indicates the timing error, the orange curve represents the filtered error at the output of the PI block, and the green curve depicts the output signal from the NCO. In this ideal scenario, the synchronization error approaches zero after an initial transient stage. The NCO output stabilizes at a value of 0.5. All curves on the *y*-axis are dimensionless.

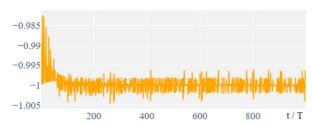

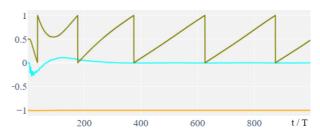

Fig. 6 focuses on the filtered error signal, offering a zoomed view. This signal follows the same profile as the error curve but appears smoother. It converges to a control value set at -1, a non-zero value selected to prevent complications from sign changes.

## 2) Scenario 1. Joint system:

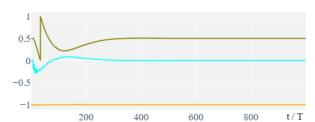

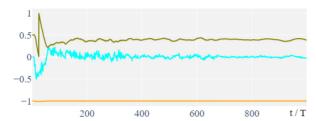

The performance curves of the joint system are plotted in Fig. 7, exhibiting similar steady-state behaviors to those of the series system but with increased smoothness.

Fig. 5. Synchronization curves for series system in the first scenario.

Fig. 6. Zoom of the filtered error for series system in the first scenario.

Fig. 7. Synchronization curves for joint system in the first scenario.

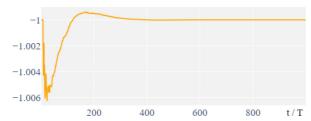

$Fig.\ 8.$  Zoom of the filtered error for joint system in the first scenario.

Fig. 8 displays a zoomed-in view of the filtered error for the joint system, which follows the same profile as the error curve. Given that this signal closely resembles the timing error and serves merely as an intermediate signal, it is omitted in subsequent scenarios to prevent redundancy.

## 3) Scenario 2. Series system:

In Fig. 9, the timing error signal approaches zero, and the filtered error signal approaches -1. Post-transient, the NCO output oscillates in a sawtooth pattern.

# 4) Scenario 2. Joint system:

Fig. 10 illustrates that the error signal approaches zero with a smooth profile. Following the transient stage, the NCO output remains periodic.

Fig. 9. Synchronization curves for series system in the second scenario.

Fig. 10. Synchronization curves for joint system in the second scenario.

## B. Low ISI channel

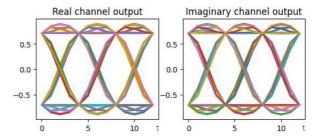

For scenarios 3 and 4, where the ISI level is 0.05, Fig. 11 depicts the channel model. The eye diagram in Fig. 12 shows some mismatching in the symbol transitions at each symbol time instant.

Fig. 11. Channel for scenarios 3 and 4: time domain and equivalent model.

Fig. 12. Eye diagram for scenarios 3 and 4.

# 1) Scenario 3. Series system:

Fig. 13 demonstrates the error signal converging to zero with moderate variability. The NCO output successfully compensates for the phase error, stabilizing at 0.5.

## 2) Scenario 3. Joint system:

Fig. 14 indicates that the joint system exhibits synchroni-

Fig. 13. Synchronization curves for series system in the third scenario.

Fig. 14. Synchronization curves for joint system in the third scenario.

Fig. 15. Synchronization curves for series system in the fourth scenario.

Fig. 16. Synchronization curves for joint system in the fourth scenario.

zation error, filtered error, and NCO output signals with fewer disturbances compared to the series system. The curves exhibit no instability peaks.

## 3) Scenario 4. Series system:

As depicted in Fig. 15, the error curve stabilizes with a zero mean, and the NCO output continues to oscillate periodically, experiencing rapid perturbations.

# 4) Scenario 4. Joint system:

Fig. 16 displays the timing error with a zero mean and the NCO output in periodic oscillation, exhibiting greater stability and smoothness than the series system.

## C. High ISI channel

This case pertains to scenarios 5 and 6, where the ISI level is 0.15. Fig. 17 illustrates the channel model, which exhibits significant dispersion, as evidenced by the pronounced peaks compared to previous examples. Subsequently, Fig. 18 displays the eye diagrams, indicating that despite the high ISI value, detection remains feasible due to the presence of eye openings.

Fig. 17. Channel for scenarios 5 and 6: time domain and equivalent model.

Fig. 18. Eye diagram for scenarios 5 and 6.

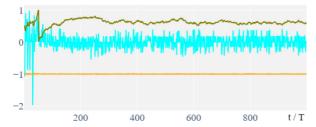

## 1) Scenario 5. Series system:

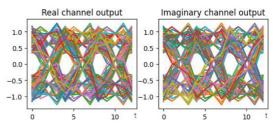

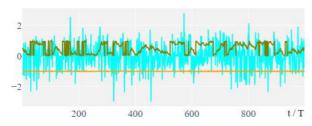

Fig. 19 presents the performance of the serial system in this scenario, where the timing error signal fluctuates around zero with highly variable peaks. The NCO output curve displays an unstable profile.

Fig. 19. Synchronization curves for series system in the fifth scenario.

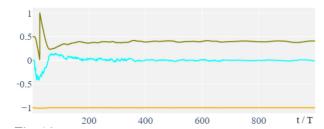

# 2) Scenario 5. Joint system:

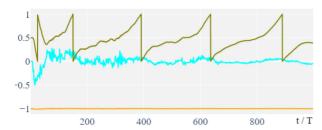

Conversely, Fig. 20 demonstrates that the system maintains normal operating behavior, as evidenced by the zero mean of the error curve. The NCO output curve appears smooth and stabilizes at the setting value of 0.5.

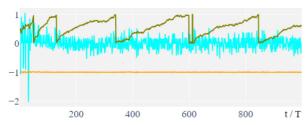

## 3) Scenario 6. Series system:

Fig. 21 depicts the error signal oscillating around zero, with occasional peaks of significant variability. The NCO output displays an erratic pattern.

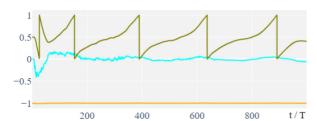

## 4) Scenario 6. Joint system:

Fig. 22 illustrates that the error signal converges to zero after the transient stage, whereas the NCO output continues to oscillate periodically, indicating proper operation.

Fig. 20. Synchronization curves for joint system in the fifth scenario.

$Fig.\ 21.$  Synchronization curves for series system in the sixth scenario.

Fig. 22. Synchronization curves for joint system in the sixth scenario.

## IV. DISCUSSION

### A. Analysis of results

Both the serial and joint systems exhibit competent performance in achieving synchronization with a constant phase error spanning a quarter of a symbol time, even in the presence of a frequency offset, as observed in scenarios 1 to 4. Additionally, the convergence times of the two systems are remarkably similar.

In the first scenario, where only the phase offset is present, the NCO output swiftly corrects this deviation during its transient stage. A detailed analysis of Figs. 5 to 8 reveals that the timing error and filtered error curves of the joint system demonstrate less variability, suggesting that the joint system achieves higher precision.

When a frequency offset is introduced alongside a phase offset, as in the second scenario, the output of the NCO is in constant frequency correction. Consequently, the resulting curve exhibits periodic oscillations similar to a sawtooth function. A comparison of Figs. 9 and 10 reveals that the joint system consistently achieves lower variability in performance.

A similar pattern is observed in scenarios 3 and 4. As depicted in Figs. 13 to 16, both the series and the joint systems successfully correct phase and frequency errors. However, notable differences in performance are evident. The series system exhibits a more pronounced degradation, characterized by increased fluctuations and irregularities in the curves. In contrast, the joint system demonstrates smoother performance, indicating its superior ability to maintain stability and accuracy.

In scenario 5, as depicted in Fig. 19, the series system struggles to maintain performance in the presence of high levels of ISI, and it encounters difficulties in achieving synchronization and consequently in recovering the correct timing of symbols. Conversely, the joint system, as illustrated in Fig. 20, is able to overcome these impairments, ensuring effective detection and synchronization.

In the final scenario, the series system is unable to effectively correct the defects caused by frequency deviation and ISI, as evidenced by the high variability in the timing error curve plotted in Fig. 21. This system fails to converge the signal to zero, leading to the propagation of erratic behavior throughout the other curves in the loop. In contrast, the joint system maintains accurate performance, as seen in Fig. 22.

These findings underscore the superior effectiveness of the joint system compared to the series system. The ability of the joint system to simultaneously address synchronization and equalization contributes to its enhanced stability and robustness in challenging communication environments.

## **B.** Conclusions

The present simulations and comparative analysis illustrate the potential benefits of the joint architecture in maintaining stable transmission, particularly in scenarios susceptible to ISI, such as when overlapping symbols distort the signal or when there is a deviation in the receiver sampling time from the transmitted symbol time. This is in comparison to the conventional approach.

A control system incorporating NCO shares several similarities with the conventional analog phase-locked loop. However, a detailed analysis of the digital implementation is crucial to avoid unforeseen performance limitations. An architecture proficient in managing synchronization issues is

essential for ensuring reliable communication, as it minimizes signal distortion and maximizes data integrity.

Further optimizations are necessary to comprehensively assess the advantages and disadvantages of this joint architecture across various communication scenarios and channel conditions. In future research, we intend to continue investigating the relationship between these systems under different parameter settings to determine the circumstances under which one system may be optimal. Additionally, the incorporation of new operating schemes will facilitate a broader comparison.

## **ACKNOWLEDGMENTS**

We would like to thank Editage (www.editage.co.kr) for English language editing. Moreover, we value the support of the National Scientific and Technical Research Council.

#### REFERENCES

- [1] F. Gardner, "A bpsk/qpsk timing-error detector for sampled receivers," *IEEE Transactions on Communications*, vol. 34, no. 5, pp. 423-429, May 1986. DOI: 10.1109/TCOM.1986.1096561.

- [2] F. Gardner, "Interpolation in digital modems. i. fundamentals," *IEEE Transactions on Communications*, vol. 41, no. 3, pp. 501-507, Mar. 1993, DOI: 10.1109/26.221081.

- [ 3 ] L. Erup, F. Gardner, and R. Harris, "Interpolation in digital modems. ii. implementation and performance," *IEEE Transactions on Communications*, vol. 41, no. 6, pp. 998-1008, Jun. 1993. DOI: 10.1109/26.231921.

- [4] H. Zhou, Y. Li, D. Lu, L. Yue, C. Gao, Y. Liu, R. Hao, Z. Zhao, W. Li, J. Qiu, X. Hong, H. Guo, Y. Zuo, and J. Wu, "Joint clock recovery and feed-forward equalization for pam4 transmission," *Optics Express*, vol. 27, no. 8, pp. 11385-11395, Apr. 2019. DOI: 10.1364/OE.27.011385.

- [5] Q. Yu, Z. Huang and J. Ba, "An Improved Gardner Feedback Timing Synchronization Loop," 2022 10th International Conference on Intelligent Computing and Wireless Optical Communications

- (ICWOC), Chongqing, China, pp. 63-67, Jun.2022. DOI: 10.1109/ICWOC55996.2022.9809870.

- [6] S. Haar, R. Zukunft, and F. Vogelbruch, "A timing recovery criterion derived from the tap weights of a decision feedback equalizer for QAM digital subscriber line systems," in 2002 14th International Conference on Digital Signal Processing Proceedings. DSP 2002 (Cat. No.02TH8628), Santorini, Greece, pp. 1281-1284, Jul. 2002. DOI: 10.1109/ICDSP.2002.1028327.

- [7] K. T. Bae, W. G. Jeon, and Y. S. Cho, "Convergence analyses of timing and carrier recovery loops for a digital communication channel with an adaptive equalizer," in *Proceedings of 40th Midwest Symposium on Circuits and Systems. Dedicated to the Memory of Professor Mac Van Valkenburg*, Sacramento, USA, pp. 1366-1369, Aug. 1997. DOI: 10.1109/MWSCAS.1997.662336.

- [8] A. Fertner and C. Solve, "Symbol-rate timing recovery comprising the optimum signal-to-noise ratio in a digital subscriber loop," *IEEE Transactions on Communications*, vol. 45, no. 8, pp. 925-936, Aug. 1997. DOI: 10.1109/26.618296.

- [9] D. Artman, S. Chari, and R. Gooch, "Joint equalization and timing recovery in a fractionally-spaced equalizer," in [1992] Conference Record of the Twenty-Sixth Asilomar Conference on Signals, Systems & Computers, Pacific Grove, USA, pp. 25-29, Oct. 1992. DOI: 10.1109/ACSSC.1992.269264.

- [10] J. Keane, M. Le, and P. Hurst, "Analog timing recovery for a noise-predictive decision-feedback equalizer," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 2, pp. 338-342, Feb. 2003. DOI: 10.1109/JSSC.2002.807171.

- [11] J. Kenney, "Multi-level decision feedback equalization with clock recovery," in [1992] Conference Record of the Twenty-Sixth Asilomar Conference on Signals, Systems & Computers, Pacific Grove, USA, pp. 945-949, Oct. 1992. DOI: 10.1109/ ACSSC.1992.269081.

- [12] A. A. Nasir, S. Durrani, and R. A. Kennedy, "Blind fractionally spaced equalization and timing synchronization in wireless fading channels," in 2010 2nd International Conference on Future Computer and Communication, Wuhan, China, pp. V3-15-V3-19, May 2010. DOI: 10.1109/ICFCC.2010.5497663.

- [13] H. Yang and L. Zhu, "Joint carrier recovery and blind decision feedback equalizer over fast time-varying channels," in 2009 International Conference on Wireless Communications Signal Processing, Nanjing, China, pp. 1-4, Nov. 2009. DOI: 10.1109/ WCSP.2009.5371743.

#### Adrián F. Ramírez

was born in Villa Mercedes, San Luis, Argentina on July 16, 1990. He graduated as electronic engineer from the National University of San Luis, Villa Mercedes in 2017. Since 2018, he is a doctoral student in engineering sciences and member of the Digital Communications Laboratory (LCD) from the Institute of Advanced Studies in Engineering and Technology of the National University of Córdoba (UNC), Córdoba, Argentina. He has published in national and international scientific journals on topics from wireless signals to satellite transmission. His research fields include communication systems and digital signal processing.

## **Felipe Pasquevich**

was born in Berisso, Buenos Aires, Argentina on August 7, 1961 and graduated as Electronics Engineer from the National University of La Plata (UNLP) in La Plata, 1993. He entered to the National Commission for Space Activities (CONAE) in 1994, participating in tests and launching the SAC-B satellite earth station. In 1995, he joined the SAC-C satellite group as Test Engineer, Flight Engineer, Chief of Operations, and Director of Mission. He served as Mission Manager of the SAC-D project and participated in reviews of SAC-D and SAOCOM 1-A missions alongside members of NASA, ASI and other space agencies. In 2018, he started to pursue his PhD and joined the LCD at the UNC. His research focuses on wireless transmission

#### **Graciela Corral Briones**

achieved her degrees in Electrical and Electronic Engineering and Ph.D. from the UNC, Córdoba, Argentina in 1991 and 2007, respectively. Between 1991 and 1993, she held the position of Research Fellow at the Center for Research in Materials in Cordoba. From 1993 to 1996, she received a fellowship from Scientific and Technological Research Council of Cordoba (CONICOR) to develop communication protocol analyzers. Since 1996, she is associated with the LCD at the Department of Electronic Engineering, UNC. Her research focuses on wireless communications and signal processing, especially multiuser detection, channel coding, and MIMO systems.