## A New SST Topology Comprising Boost Three-Level AC/DC Converters for Applications in Electric Power Distribution Systems

Luciano A. Garcia Rodriguez, *Student Member, IEEE*, Vinson Jones, *Student Member, IEEE*, Alejandro R. Oliva, Andrés Escobar-Mejía, *Member, IEEE*, and Juan C. Balda, *Senior Member, IEEE*

Abstract—The growing interest in integrating distributed generation (DG) into the existing power distribution grid, the increase in the penetration levels of renewables, as well as the need to achieve a more efficient, reliable and sustainable grid, are leading to the development of new grid-interfaced power converters such as the solid-state transformer (SST). As current and voltage ratings of commercially available power semiconductor devices are normally below power ratings required in distribution systems (e.g., 13.8 kVrms), multiple modules must be connected in cascade configuration at the high-voltage side to reach higher voltage ratings as well as in parallel at the low-voltage side to achieve high current levels.

A new SST topology consisting of modular boost-based three-level ac-dc converters, medium-frequency transformers with two secondary windings, and four-leg ac-dc converters is presented in this paper. When compared to similar approaches, the proposed topology comprises fewer power conversion stages, lower voltage across the semiconductor devices on the high-voltage side, and lower current flowing through each device on the low-voltage side. These characteristics reduce the number of series-connected modules in the high-voltage side and parallel-connected devices in the low-voltage side. The feasibility of the proposed topology is experimentally validated on a 500 W, 120 Vac/ 48 Vdc scaled-down prototype.

Index Terms— Boost-based topology, four-leg dc-ac converter, multi-winding solid-state transformer (SST), three-level dc-ac converter.

### I. INTRODUCTION

During the last decades, factors such as changes in the power grid structure, the increase of penetration levels of renewables, the implementation of dc grids, and the need to offer premium power quality to customers have motivated

Manuscript received April 4, 2016; revised June 2, 2016, August 8, 2016 and November 15, 2016; accepted February 10, 2017.

L. A. Garcia Rodriguez, V. Jones, and J. C. Balda are with the Department of Electrical Engineering, University of Arkansas, Fayetteville, AR 72701 USA (e-mail: lgarciar@uark.edu, vjjones@email.uark.edu; jbalda@uark.edu).

A. R. Oliva is with the Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET) and with the Instituto de Investigaciones en Ingeniería Eléctrica "Alfredo Desages," Departamento de Ingeniería Eléctrica y Computadoras, Universidad Nacional del Sur (UNS), Bahía Blanca, 8000, Argentina (e-mail: aoliva@uns.edu.ar).

A. Escobar-Mejia is with La Universidad Tecnológica de Pereira, Risaralda, Colombia, CO 660004 (e-mail: andreses1@utp.edu.co).

utilities to implement new power electronic interfaces (PEI) to modernize the conventional power distribution system. One of the most helpful and promising PEI in future power grids is the so-called solid-state transformer (SST), which has been proposed to replace the bulky fundamental-frequency transformers for several applications [1]–[7]. In addition to the functionalities of conventional transformers (e.g., galvanic isolation between networks and voltage matching between two voltage levels), the SST is capable of controlling the power flow between networks, limiting fault currents, integrating energy storage units, compensating for reactive power, improving power quality, and many others. These assets make the SST a promising technology in future smart grids at any voltage and power level [3]–[5].

There have been several topologies suggested for SSTs [8]-[10]. However, the three-stage approach consisting of an ac-dc front-end side, a dual active bridge (DAB) with a high- or medium-frequency transformer (HF- or MF-XFMR) to step down or up the input voltage [11], [12], and a back-end side incorporating dc-ac or dc-dc converters for 50/60 Hz or dc loads, respectively, have been the most evaluated. To interface directly with a distribution system (from 2.3 kV to 35 kV single-phase feeders), several converters are connected in a cascaded H-bridge multilevel configuration at the front-end or high-voltage (HV) side [8], [9]. This configuration allows the use of commercially available power semiconductor devices with medium breakdown voltages (e.g., 4.5 kV and 6.5 kV IGBT) and has less current harmonic distortion at the ac side, which in turn reduces filter requirements at the system connecting point. Complex voltage balancing control methods are required to keep the dc-link voltage in the H-bridges constant [13], [14]. At the back-end side or low-voltage (LV) side several modules are connected in parallel to achieve the current rating imposed by the load. The dc bus can potentially be used to connect a dc distribution system involving distributed generation (DG) units (e.g., photovoltaic panels, energy storage, etc.) and dc loads (e.g., dc buildings, data centers, battery-charging stations, etc.). Depending on the output voltage and power level, Si and SiC MOSFETs or IGBTs are used for the LV side bridge.

Usually, dc loads are fed from three-phase power factor correction (PFC) rectifiers connected to the power grid though a medium-to-low voltage, fundamental-frequency transformer.

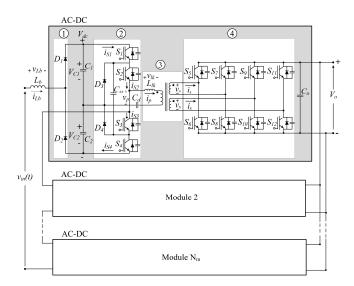

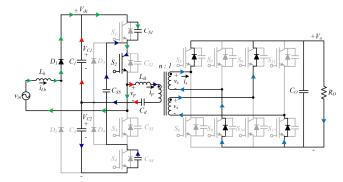

Fig. 1. Boost-based three-level SST topology with high-voltage ac input (e.g.,  $7.2~\mathrm{kV}$ ) and a low-voltage dc output (e.g.,  $400~\mathrm{V}$ ).

However, single-phase SST topologies connected to the medium-voltage grid and composed of a rectifier stage and a DAB stage are used for dc applications to eliminate the use of the low-frequency transformers [15]. The DAB stage is commonly implemented with full-bridges on primary and secondary sides [12], [16]; half-bridges on primary and secondary sides [6], or a half-bridge on primary (HV) side and a full-bridge on the secondary (LV) side [9]. To reduce the required number of conversion stages, a unidirectional SST topology based on a boost converter PFC stage [17], [18] requiring reduced number of devices by combining the rectifier stage with the primary side bridge of the DAB was presented in [9]. However, it is not suitable for applications with variable output power since it is required to operate the primary side of the DAB with a fixed 50% duty cycle. This means that a fixed 50% duty cycle will be applied to a boost inductor operating at discontinuous conduction mode (DCM), which sets a limit for the minimum output power delivered. A three-phase, three-level, unidirectional, boost-based ac-dc converter that combines a three-phase PFC rectifier stage with the primary side of a three-level isolated converter with a diode bridge at the output was presented in [19]. The threelevel waveform at the primary side of the DAB transformer allows the user to set the desired duty cycle for the PFC boost inductor operating at DCM, so the input power can be controlled. The problem with this topology is that it is not possible to control the intermediate primary side voltage and the output voltage at the same time. Therefore, the bus voltage will fluctuate depending on load conditions from a low value defined by the limit of continuous conduction (CCM) of the boost inductor to a much higher voltage at light loads. This requires the overrating of the active devices, which is not suitable for HV applications.

To solve the issues of the previous mentioned topologies, this paper presents a new SST topology with a reduced number of series-connected stages on the front-end side [20]. The proposed topology, illustrated in Fig. 1, is suitable for

applications where power flows in one direction, such as debuildings and server farms, while keeping other functionalities of a fully-featured SST. As shown, it comprises a boost-based three-level converter stage, a high-frequency (HF) or medium-frequency (MF) transformer with two secondary windings, and a four-leg full-bridge rectifier. The use of the two secondary windings makes the new topology suitable for LV and high-power applications such as information technology applications. This topology allows to fully control the primary-side dc link as well as the output voltages with the possibility to operate the converter with zero-voltage switching (ZVS) and quasi-zero-current switching (quasi-ZCS) for the whole operating power range.

The paper is organized as follows: An analysis of the proposed topology including the new topology general description, component sizing, and steady-state operating intervals is presented in Section II. Then, soft-switching operation, selection of duty cycles, phase-shift and control strategy is shown in Section III. The design procedure is presented in Section IV; and lastly, the feasibility of the proposed solution is validated through experimental results in Section V.

### II. ANALYSIS OF THE BOOST TOPOLOGY

### A. SST Topology General Description

The single-phase boost-based three-level SST topology illustrated in Fig. 1 comprises four stages for converting a higher ac voltage into a lower dc voltage. The input boost inductor  $L_h$  is designed to operate in the discontinuous conduction mode (DCM). The fact that the inductor's peak current is proportional to the input voltage allows for a high power factor at the input [21], [22]. At the front-end, a cascaded multilevel ac-dc converter is adopted (1) to accomplish high input voltage levels. A three-level neutralpoint-clamped dc-ac converter ((2)) is used to interface with the primary side of the HF- or MF-XFMR ((3)). The power semiconductor devices sustain only half of the module dc link voltage due to the three-level half-bridge configuration [23], facilitating the selection of devices having lower breakdown voltages which can operate at higher switching frequencies. The transformer is designed to have two secondary windings, which reduces the current stresses on the secondary side devices. Each secondary of the transformer is connected to a full-bridge ac-dc converter (4). A single secondary and conventional full-bridge may be used, however, the four-leg full-bridge configuration enables the use of devices with lower rated currents. Furthermore, several modules are connected in parallel to the LV dc link. The use of a full-bridge transistor configuration instead of a full-bridge diode rectifier allows to fully control dc link voltage  $V_{dc}$ , which otherwise changes depending on load conditions.

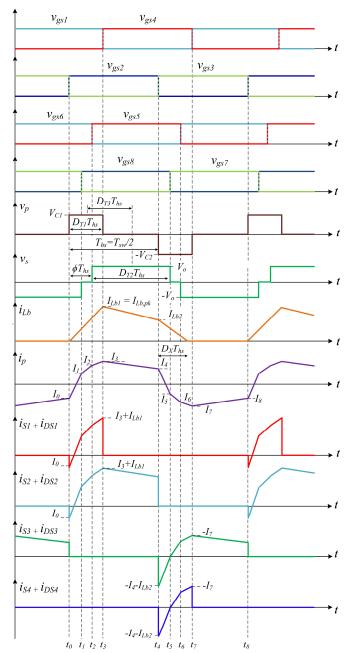

The modulation scheme for the three-level dc-ac converter is presented in Fig. 2. This scheme allows for two different three-level voltages; one applied to the primary side  $(v_p)$  and the other to the secondary side  $(v_s)$  of the transformer [24], [25]. The phase-shift between  $v_p$  and  $v_s$  is defined as  $\phi T_{hs}$ ,

Fig. 2. Theoretical waveforms of the proposed topology.

where  $T_{hs}$  corresponds to half a switching period  $(T_{sw}/2)$ .

The phase-shift between the fundamental components of  $v_p$  and  $v_s$  is  $D_{T3}T_{hs}$  which can be expressed in terms of the duty cycles and the phase-shift  $\phi$  as:

$$D_{T3} = \phi + \frac{D_{T2}}{2} - \frac{D_{T1}}{2} \,. \tag{1}$$

The time instant where the primary and secondary voltages are not equal to zero are defined as  $D_{TI}T_{hs}$  and  $D_{T2}T_{hs}$ , respectively. As explained later, the duty cycles  $D_{TI}$  and  $D_{T2}$  and the fundamental phase-shift  $D_{T3}$  are used to control the dc link voltage ( $V_{dc}$ ) and output voltage ( $V_o$ ). The duty cycles  $D_{TI}$  and  $D_{T2}$  can vary from 0 to 1 while the phase-shift  $D_{T3}$  can change from 0 to 0.5. With this modulation scheme, it is possible to obtain eight commutation intervals during a switching cycle, as illustrated in Fig. 3.

As shown in Fig 2, the boost inductor  $L_b$  is charged during  $D_{T1}T_{hs}$  when both  $S_1$  and  $S_2$  are on (for  $v_{in}(t) > 0$ ). The switches  $S_3$  and  $S_4$  facilitate the inductor charging process when  $v_{in}(t) < 0$ . For the sake of the analysis, only the positive cycle of the 60 Hz input grid voltage is considered.

In the case of series connected primaries and parallel connected secondaries, ideally all converters will operate the exact same way as a single converter. Any voltage variance among the primary dc buses would need to be corrected by modifying the power output of each separate converter using the phase-shift control.

### B. Steady-State Operating Intervals

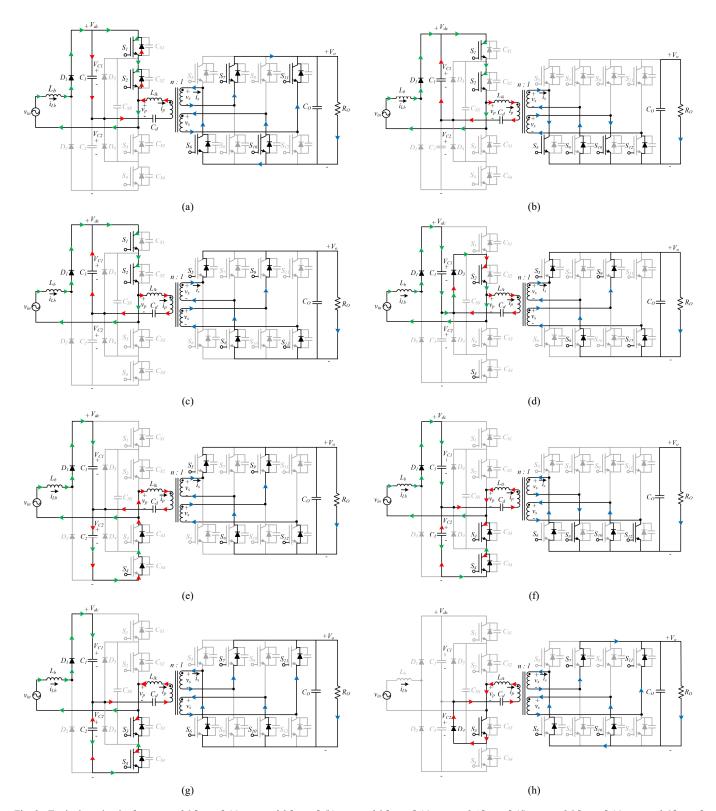

Interval  $I[t_0 - t_I]$ : Initially, the transformer primary side current  $(i_p)$  is negative and flows through the capacitor  $C_I$  and the antiparallel diodes of  $S_I$  and  $S_2$ . When  $S_I$  and  $S_2$  are both on, the boost inductor current  $(i_{Lb})$  increases linearly in time at a rate of  $v_{in}(t)/L_b$ . In this interval, the capacitor voltage  $(v_{CI})$  is applied to the primary side of the transformer. The voltage across one of the transformer's secondary windings is  $-V_o$  and the current flowing through them is  $i_s$ . When this current is negative, it flows through the antiparallel diodes of  $S_6$ ,  $S_7$ ,  $S_{I0}$  and  $S_{II}$ . When positive, it flows through the corresponding IGBTs.

Moreover, the voltage across the leakage inductance  $(v_{lk})$  is calculated as  $V_{CI} + nV_o$ , where  $n = N_p/N_s$  is the turns ratio of the HF transformer. Because  $v_{lk}$  is positive,  $i_p$  increases with a constant slope.

During this interval, the current  $i_p$  is

$$i_p(t) = I_0 + \frac{V_{C1} + nV_O}{L_{lk}} (t - t_0),$$

(2)

where  $L_{lk}$  is the transformer's leakage inductance and the initial condition  $I_o$  is calculated as follows:

$$I_0 = -\frac{nV_O}{4f_{sw}L_{lk}} \left( -2 + D_{T1} + \frac{V_{C1}}{nV_O} D_{T1} + 2D_{T3} \right), \quad (3)$$

where  $V_{CI} = V_{C2} = V_C = V_{dc}/2$ . A constant m is defined as the voltage conversion ratio  $m = nV_o/V_C$ . When m > 1, the converter is operating in boost mode and when m < 1, the converter operation is in buck mode. In this paper, the buck mode of operation is of interest.

From Fig. 2, the duration of *interval 1* is given by:

$$t_1 - t_0 = \left(\frac{D_{T1}}{2} + \frac{D_{T2}}{2} + D_{T3} - 1\right) T_{hs}$$

(4)

Interval 2 [ $t_1 - t_2$ ]: At  $t_I$ , switches  $S_7$  and  $S_{II}$  turn completely off and the antiparallel diodes of the switches  $S_8$  and  $S_{I2}$  become forward biased, bringing  $v_s$  to zero. This interval defines the zero for the three-level secondary voltage whose duration is  $(1 - D_{T2})T_{hs}$ . The current flowing through the upper secondary winding is conducted by  $S_6$  and the antiparallel diode of  $S_8$ , whereas the current flowing through the lower secondary winding is conducted by  $S_{I0}$  and the antiparallel diode of  $S_{I2}$ . The voltage  $v_{Ik}$  is equal to  $V_{CI}$ , thus  $i_p$  is:

Fig. 3. Equivalent circuits for: interval I [ $t_0 - t_1$ ] (a), interval 2 [ $t_1 - t_2$ ] (b), interval 3 [ $t_2 - t_3$ ] (c), interval 4 [ $t_3 - t_4$ ] (d), interval 5 [ $t_4 - t_5$ ] (e), interval 6 [ $t_5 - t_6$ ] (f), interval 7 [ $t_6 - t_7$ ] (g), interval 8 [ $t_7 - t_8$ ] (h).

$$i_{p}(t) = I_{1} + \frac{V_{C1}}{L_{lk}}(t - t_{1}), \qquad (5)$$

$$I_{1} = -\frac{nV_{O}}{4f_{sw}L_{lk}} \left(\frac{V_{C1}}{nV_{O}}(2 - D_{T2} - 2D_{T3}) - D_{T2}\right). \qquad (6)$$

where the initial condition  $I_I$  is calculated as:

*Interval 3* [ $t_2 - t_3$ ]: The switches  $S_6$  and  $S_{10}$  turn off at  $t_2$  and

$i_s$  is conducted by the antiparallel diodes of  $S_5$ ,  $S_8$ ,  $S_9$  and  $S_{I2}$ . The output voltage is applied to the secondary windings of the transformer, thus  $v_{lk}$  is equal to  $V_{CI} - nV_o$ . For the theoretical waveforms presented in Fig. 2,  $V_{CI}$  is larger than  $nV_o$  and  $i_p$  keeps increasing as:

$$i_p(t) = I_2 + \frac{V_{C1} - nV_O}{L_{lk}}(t - t_2),$$

(7)

where the initial condition  $I_2$  is equal to:

$$I_2 = -\frac{nV_O}{4f_{sw}L_{lk}} \left( \frac{V_{C1}}{nV_O} (D_{T2} - 2D_{T3}) - D_{T2} \right).$$

(8)

The duration of this interval can be determined as:

$$t_3 - t_2 = (D_{T1} - \varphi)T_{hs} = \left(D_{T1} - \frac{D_{T2}}{2} + D_{T3}\right)T_{hs}.$$

(9)

Interval 4  $[t_3 - t_4]$ : This interval determines the duration for the zero state of the transformer primary side,  $(I - D_{TI})T_{hs}$ . After  $S_I$  turns off, the current flowing through the freewheeling diode  $D_3$  is equal to  $i_p$  plus the current of the boost inductor, which gets discharged through  $C_I$ . The voltage applied to the leakage inductance is negative and  $i_p$  decreases as:

$$i_p(t) = I_3 - \frac{nV_o}{L_{lk}}(t - t_3),$$

(10)

where the initial condition  $I_3$  is calculated as:

$$I_3 = \frac{nV_O}{4f_{sw}L_{lk}} \left( \frac{V_{C1}}{nV_O} D_{T1} - D_{T1} + 2D_{T3} \right)$$

(11)

At the end of this interval  $t = T_{sw}/2$ .

Interval 5 [ $t_4 - t_5$ ]: After  $S_2$  is turned off, the currents  $i_p$  and  $i_{Lb}$  flow through the antiparallel diodes of  $S_3$  and  $S_4$ . The energy stored in the boost inductor  $L_b$  is transferred to capacitors  $C_1$  and  $C_2$  and the voltage applied to the primary side of the transformer is  $-V_{C2}$ . Thus, the primary current is:

$$i_p(t) = I_4 - \frac{V_{C2} + nV_O}{L_{lk}} (t - t_4),$$

(12)

where  $I_4$  is equal to  $I_0$ . If during this interval, the transformer current changes its polarity, the current is conducted through  $S_3$  and  $S_4$  in the primary side and through  $S_5$ ,  $S_8$ ,  $S_9$  and  $S_{12}$ , in the secondary side, respectively.

Interval 6 [ $t_5 - t_6$ ]: This interval takes place after  $S_5$  and  $S_9$  turn off. The voltage  $v_s$  is equal to zero and the upper winding current  $i_s$  flows through the antiparallel diode of  $S_6$  and the switch  $S_8$ , whereas the lower winding current flows through the antiparallel diode of  $S_{10}$  and the switch  $S_{12}$ . In this interval, the boost inductor keeps discharging through the capacitors  $C_1$  and  $C_2$ . The primary winding current is calculated as:

$$i_p(t) = I_5 - \frac{V_{C2}}{L_{lk}}(t - t_5),$$

(13)

where  $I_5$  is equal to  $-I_1$ .

Interval 7 [ $t_6 - t_7$ ]: The switches  $S_8$  and  $S_{12}$  turn off and the antiparallel diodes of  $S_6$  and  $S_7$  conduct  $i_s$  for the upper winding whereas the antiparallel diodes of  $S_{10}$  and  $S_{11}$  conduct

TABLE I

PEAK AND RMS CURRENTS

| Boost Inductor Current                                                                                                                                                                                                                                                                     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| $I_{Lb,rms} = \frac{V_{C1}}{\sqrt{8\pi}L_b f_{sw}} \sqrt{\int_0^{\phi_{cl}} \left(\frac{D_{T1}^2 \sin \omega t}{g - 2 \sin \omega t}\right)^2 d\omega t} + \int_{\phi_{ss}}^{\pi/2} \left(\frac{2(D_{T1}^2 + 1) \sin \omega t - g(D_{T1} - 1)^2}{4(g - \sin \omega t)}\right)^2 d\omega t$ |  |  |

| $I_{Lb,pk} = \frac{V_{pk}T_{sw}}{2L_b}$                                                                                                                                                                                                                                                    |  |  |

### Rectifier Diode Current

$$I_{_{D1,RMS}}=I_{_{D2,RMS}}=\frac{I_{_{Lb,RMS}}}{\sqrt{2}}$$

$$I_{D1,pk} = I_{D2,pk} = I_{Lb,pk}$$

#### Switch Current

$$\begin{split} I_{_{S1,RMS}} &= I_{_{S4,RMS}} \cong \frac{I_{_{3}}D_{_{71}}}{2\sqrt{2}} + \frac{V_{_{pk}}D_{_{71}}^{2}}{16L_{_{b}}f_{_{sw}}} \\ I_{_{S2,RMS}} &= I_{_{S3,RMS}} \cong \frac{I_{_{Lb,RMS}}}{2} + \frac{I_{_{3}}}{2\sqrt{2}} \\ I_{_{S1,pk}} &= I_{_{S2,pk}} = I_{_{S3,pk}} = I_{_{S4,pk}} = I_{_{3}} + I_{_{Lb,pk}} \end{split}$$

# $I_{SS,pk} = I_{S6,pk} = I_{S7,pk} = I_{S8,pk} = I_{S9,pk} = I_{S10,pk} = I_{S11,pk} = I_{S12,pk} = \frac{nI_3}{2}$ Free-Wheeling Diode Current

$$I_{D3,RMS} = I_{D4,RMS} = I_3 \sqrt{\frac{1 + D_{71}^2}{32}}$$

$$I_{D3,pk} = I_{D4,pk} = I_3 + I_{Lb,pk}$$

the currents for the lower winding. In this interval, the boost inductor current goes to zero and the primary current is calculated as:

$$i_p(t) = I_6 + \frac{-V_{C2} + nV_o}{L_w} (t - t_6),$$

(14)

where  $I_6$  is equal to  $-I_2$ .

Interval 8  $[t_7 - t_8]$ : After  $S_4$  turns off, the current  $i_p$  freewheels through  $S_3$  and  $D_4$  while  $i_s$  is conducted by the diodes of  $S_6$ ,  $S_7$ , and  $S_{10}$ ,  $S_{11}$  for the upper and lower windings, respectively. The primary current is then given by:

$$i_p(t) = I_7 + \frac{nV_o}{L_n}(t - t_0),$$

(15)

where  $I_7$  is equal to  $-I_3$ .

### C. Efficiency Model

Table I summarizes the expressions for the peak and RMS currents of the semiconductors.

### D. Power Factor (PF) Calculation

When the input current is discontinuous, the peak of the inductor current follows the ac input voltage waveform. However, when the boost inductor discharges, there is a distortion introduced by the modulation of the off time [22]. In the case of the proposed converter, the inductor current will discharge with one or two slopes depending on the applied level of the ac input voltage and the duty cycle  $D_{TI}$ , as shown

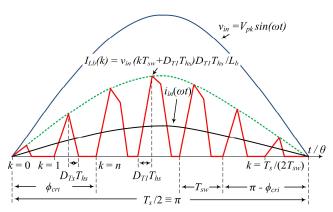

Fig. 4. Graphical representation of the input boost inductor current.

in Fig. 4. The critical angle  $\phi_{cri}$ , which defines the limit between the operations with one or two slopes, is calculated as [19]:

$$\phi_{cri} = \sin^{-1} \left[ \frac{g}{2} (1 - D_{T1}) \right],$$

(16)

where  $g = V_{dc}/V_{pk}$ .

The average boost inductor current is calculated considering the intervals where the current has one or two slopes:

$$i_{in}(\omega t) = \begin{cases} i_{in1}(\omega t) & 0 < \theta < \phi_{cri} & and & \pi - \phi_{cri} < \theta < \pi \\ i_{in2}(\omega t) & \phi_{cri} < \theta < \pi - \phi_{cri} \end{cases},$$

where:

$$i_{in1}(\omega t) = \frac{D_{T1}^2 V_{C1}}{4L_b f_{sw}} \frac{\sin \omega t}{g - \sin \omega t},$$

$$i_{in2}(\omega t) = \frac{V_{C1}}{16L_b f_{sw}} \frac{2(D_{T1}^2 + 1)\sin \omega t - g(D_{T1} - 1)^2}{g - \sin \omega t}.$$

(17)

Then, the average input power is calculated as:

$$P = \frac{2}{\pi} \left[ \int_{0}^{\phi_{cri}} v_{in}(\omega t) i_{in_{-1}}(\omega t) d\omega t + \int_{\phi_{cri}}^{\pi/2} v_{in}(\omega t) i_{in_{-2}}(\omega t) d\omega t \right],$$

$$P = \frac{V_{pk}V_{C1}}{\pi L_b f_{sw}} \begin{bmatrix} \int_{0}^{\varphi_{C1}} \frac{D_{T1}^2 \sin^2 \omega t}{2(g - 2\sin \omega t)} d\omega t + \\ \int_{0}^{\pi/2} \frac{2(D_{T1}^2 + 1)\sin^2 \omega t - g(D_{T1} - 1)^2 \sin \omega t}{8(g - \sin \omega t)} d\omega t \end{bmatrix} . (18)$$

The *PF* is calculated as:

$$PF = \frac{P}{S}$$

,

where the per-phase apparent power is equals to  $V_{rms}I_{rms}$ . Then, the PF is expressed as:

$$PF = \frac{2}{\sqrt{\pi}} \frac{\int_{0}^{\theta_{r1}} \frac{D_{T1}^{2} \sin^{2} \omega t}{g - 2\sin \omega t} d\omega t + \int_{\theta_{rr}}^{\pi/2} \frac{2(D_{T1}^{2} + 1)\sin^{2} \omega t - g(D_{T1} - 1)^{2} \sin \omega t}{4(g - \sin \omega t)} d\omega t}{\sqrt{\int_{0}^{\theta_{r1}} \left(\frac{D_{T1}^{2} \sin \omega t}{g - 2\sin \omega t}\right)^{2} d\omega t + \int_{\theta_{rr}}^{\pi/2} \left(\frac{2(D_{T1}^{2} + 1)\sin \omega t - g(D_{T1} - 1)^{2}}{4(g - \sin \omega t)}\right)^{2} d\omega t}}.$$

(19)

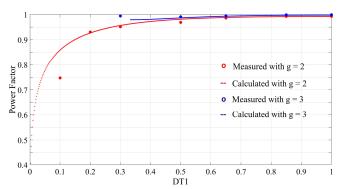

Fig. 5 presents the plot of the calculated and measured power factors as function of  $D_{TI}$  when g changes from 2 to 3. It is possible to see that the power factor is close to 1 when the dc link voltage  $V_{dc}$  is much higher than the peak of the input ac

voltage and a large  $D_{Tl}$ . Also for small duty cycles, and thus small input power, the power factor is low. It can be seen from (16) that the selection of g limits the minimum  $D_{Tl}$  that the converter can operate:

$$D_{T1} > 1 - \frac{2}{g}. (20)$$

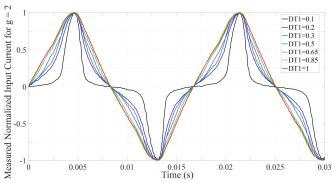

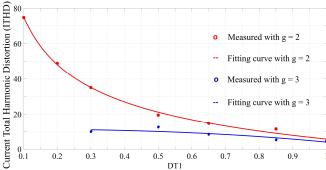

IEEE Std. 519-2014 [26] limits the harmonic distortion of the current that a load takes from the utility grid at the point of common coupling (PCC). Table II in [26] sets the limits for the individual harmonic current distortion and the total demand distortion (TDD) in percent of fundamental current up to the 50th harmonic of the line frequency. Fig. 6 shows the measured input current for different values of  $D_{TI}$  where it can be seen that the current gets distorted when  $D_{Tl}$  is small. TDD is evaluated at the maximum demand load current; when the SST operates under this condition the PF is larger than 0.99 and the ITHD is smaller than 14% as shown in Fig. 7. According to Table II of [26] this SST may be used at locations where  $I_{sc} / I_L$  is larger than 50. The high frequency components related to the switching frequency are considered electromagnetic interference (EMI) and should be attenuated by an EMI filter determined according IEC 61000 standard.

### E. SST Topology Design Equations

### 1) Boost inductor design

The boost inductor is designed to operate in the DCM, which intrinsically provides a high power factor (as long as the dc bus voltage is kept larger than twice the peak of the line voltage [22]) since the instantaneous peak inductor current is proportional to the input voltage. The positive cycle of the input ac voltage and DCM operation are considered for the analysis. The inductor  $L_b$  is sized considering the worst case scenario, which occurs when the input voltage and output power are maximum and the maximum duty cycle is applied. Therefore, the case where the primary duty cycle is maximum  $(D_{TI} = 1)$  is considered so the zero state is eliminated and the inductor will be discharged only through the series combination of  $C_I$  and  $C_2$ .

Thus, the dc bus capacitors are both charged to  $V_{pk}$  and the critical condition for the inductor to operate in DCM is:

$$L_{b\_critic} = \frac{V_{pk}^2}{8f_{sw}P_{o \text{ max}}}.$$

(21)

where  $P_{o\_max}$  is the maximum output power. Then,  $L_b$  should be chosen to be less than  $L_b$  critic.

### 2) HV dc link capacitor voltage

The gain from the ac input voltage to the HV dc bus capacitors can be approximated by considering that the ac input voltage has an imperceptible variation with respect to the high switching frequency and the values of  $C_I$  and  $C_2$  are large enough to sustain the voltage level at which they are charged. In that case, the steady-state analysis gives the following relationship where  $D_{TI}$  is the duty cycle defined as the time interval where  $S_I$  and  $S_2$  are on  $(S_3$  and  $S_4$  if  $v_{in}(t)$  is in its negative cycle) and  $D_{Tx}T_{hs}$  is the time that it takes for the boost

Fig. 5. Measured and calculated input power factor as function of the duty cycle  $D_{TI}$  and for different values of g.

Fig. 6. Input current as function of the duty cycle  $D_{TI}$  when g equals 2.

Fig. 7. Input current as function of the duty cycle  $D_{TI}$  when g equals 2.

inductor current to reach zero when  $S_3$  and  $S_4$  are on ( $S_1$  and  $S_2$  if  $v_{in}(t)$  is in its negative cycle).

$$\frac{V_C}{V_{pk}} = \frac{1/2 + D_{Tx}}{1/2 - D_{T1} + 2D_{Tx}} \ . \tag{22}$$

From (22), the capacitor  $C_1$  and  $C_2$  voltage levels are at least  $V_{pk}$  when  $D_{Tx}$  equals  $D_{Tl}$ . Then,  $V_{dc} = V_{C1} + V_{C2} \ge 2V_{pk}$ .

### 3) Minimum and maximum input power

g and the minimum  $D_{TI}$  are selected (see Fig. 5, 6 and 7) for the situation that determines the minimum input power for the converter to operate at DCM, based on the desired operating input power factor and current harmonic distortion. The minimum input power for the converter is derived from the calculation of the boost inductor energy over half of the fundamental-frequency period. The energy stored in the inductor at each switching interval depends on the peak inductor current which is a function of the input voltage at

each switching interval and the on time. Therefore, the instantaneous peak inductor current is equal to:

$$I_{Lb}(k) = \frac{v_{in}(kT_{sw} + D_{T1}T_{hs})D_{T1}T_{hs}}{L_{h}},$$

(23)

7

where  $v_{in}(kT_{sw} + D_{T1}T_{hs}) = V_{pk} \sin((2\pi/T_s)(kT_{sw} + D_{T1}T_{hs}))$  and k an integer indicating the number of switching cycles that have occurred since the zero crossover point of the input voltage.

Then, the energy at each time instant is expressed as:

$$E_k = \frac{1}{2} \frac{(D_{T1} T_{hs})^2}{L_b} V_{pk}^2 \sin^2 \left( \frac{2\pi}{T_s} (k T_{sw} + D_{T1} T_{hs}) \right). \tag{24}$$

The total energy during half cycle of the grid voltage is equal to the summation of the energies over half a period:

$$E_{half\_cycle} = \sum_{k=0}^{T_s/2T_{sw}} \frac{(D_{T1}T_{hs}V_{pk})^2}{2L_b} \sin^2\left(\frac{2\pi}{T_s}(kT_{sw} + D_{T1}T_{hs})\right),$$

(25.a)

which becomes:

$$E_{half\_cycle} = \frac{(D_{T1}T_{hs}V_{pk})^2 A}{4L_{h}},$$

(25.b)

where:

$$A = \left[ \frac{T_s}{2T_{sw}} - \frac{\cos(\pi (1 + 4D_{T_1}T_{hs} / T_s))\sin(\pi (1 + 2T_{sw} / T_s))}{\sin(2\pi T_{sw} / T_s)} \right].$$

(25.c)

Then, the minimum input power can be calculated by dividing (25.b) by half of the input-voltage fundamental period:

$$P_{in\_min} = \frac{(D_{T1}T_{hs}V_{pk})^2}{2T.L_t} A, \qquad (26)$$

where  $T_s$  is the line period.

The maximum input power can be derived from (18) by inserting  $D_{TI} = 1$ , which determines  $\phi_{cri} = 0$ . Under those conditions, the maximum input power is approximated as:

$$P_{in\_max} = \frac{V_{pk}V_C}{2\pi L_b f_{sw}} \left[ \int_0^{\pi/2} \frac{\sin^2 \omega t}{g - \sin \omega t} d\omega t \right]$$

$$\approx \frac{V_{pk}V_C}{2\pi L_b f_{sw}} (35.29e^{-2.691g} + 1.153e^{-0.3885g}).$$

(27)

### 4) Output power and voltage

The output power of the converter is calculated by integrating over half the switching period the product of the primary current  $i_p$  and the primary voltage  $v_p$ :

$$P_{out\_max} = \frac{2}{T_{sw}} \int_{0}^{T_{sw}/2} v_p(t) i_p(t) dt$$

$$= \frac{V_C n V_o}{4 f_{cw} L_{tv}} \left( D_{T1} + D_{T2} + 2D_{T3} - \frac{D_{T1}^2}{2} - \frac{D_{T2}^2}{2} - 2D_{T3}^2 - 1 \right).$$

(28)

It can be seen that the maximum power transferred occurs when  $D_{TI} = D_{T2} = 1$  and the phase-shift  $D_{T3} = 0.5$ .

The output voltage is found by expressing the output power

as a function of the output voltage and the resistive load:

$$V_o = \frac{V_C nR_o}{4f_{sw}L_{lk}} \left( D_{T1} + D_{T2} + 2D_{T3} - \frac{D_{T1}^2}{2} - \frac{D_{T2}^2}{2} - 2D_{T3}^2 - 1 \right),$$

(29)

where  $R_o$  corresponds to the load resistance.

### III. OPTIMAL SELECTION OF DUTY CYCLES AND PHASE-SHIFT FOR SOFT-SWITCHING AND CONTROL

In this section, the optimal selection of the duty cycles and the phase-shift for the proposed converter is presented. From (26), it is clear that the input power depends on the primary side duty cycle  $D_{TI}$  while the transferred power (28) is governed by  $D_{TI}$ ,  $D_{T2}$  and  $D_{T3}$ . However,  $D_{T3}$  has more of an effect in (28) than  $D_{TI}$  or  $D_{T2}$ . Therefore,  $D_{TI}$  is used to control the dc bus voltage  $V_{dc}$  controlling the input power while  $D_{T3}$  is selected to control the output voltage  $V_o$  controlling the transferred power. The selection of the secondary side duty cycles is discussed later in this section.

### A. Mode Constraints

Different modes of operation arise depending if the duty cycles of the primary and secondary side voltages have partial overlaps, no overlaps or full overlaps. The mode of operation represented in Fig. 2 with partially overlapping voltage waveforms is selected because it is capable of transferring the maximum power with soft-switching operation for all devices. The restrictions that need to apply to stay in the mode shown in Fig. 2 are:

$$D_{T3} \le \frac{D_{T1}}{2} + \frac{D_{T2}}{2} \,, \tag{30}$$

$$D_{T2} \ge 2\left(1 - \frac{D_{T1}}{2} - D_{T3}\right),\tag{31}$$

$$D_{T2} \ge 1 - D_{T1} \,. \tag{32}$$

### B. Soft-Switching Analysis

At turn on, zero voltage switching (ZVS) is achieved for all operating intervals if the polarity of the transformer current is correct. Moreover, the capacitors connected in parallel with the switches enable quasi-ZCS at turn off. Only the transition between *intervals 3* and 4 is analyzed in this paper because similar processes occur for other devices. The conditions for the transformer current that allows soft-switching operation in all devices are presented in Table II.

Initially,  $S_I$  and  $S_2$  conduct  $i_{Lb}$  and  $i_p$  (see Fig. 3(c)). The capacitor  $C_{ss}$  and the parasitic capacitors of  $S_3$  and  $S_4$  are charged up to  $V_C = V_{CI} = V_{C2}$ . As soon as  $S_I$  turns off, the current that was flowing through  $S_I$  conducts though  $S_I$  (turning  $S_I$  off at quasi-ZCS) and charges it.  $S_I$  and  $S_I$  are connected by  $S_I$  whose voltage is almost constant due to its quite large value (1µF), in comparison with  $S_I$  and  $S_I$  (Fig. 8). Therefore, the voltage across  $S_I$  increases as much as the voltage across  $S_I$  decreases. When  $S_I$  reaches the level of

TABLE II ZVS AND QUASI-ZCS CONDITIONS

| Before the Starting of: | Condition |

|-------------------------|-----------|

| $t_0-t_I$               | $I_0 < 0$ |

| $t_1-t_2$               | $I_I > 0$ |

| $t_2 - t_3$             | $I_2 > 0$ |

| $t_3-t_4$               | $I_3 > 0$ |

| $t_4-t_5$               | $I_4 > 0$ |

| $t_5-t_6$               | $I_5 < 0$ |

| $t_6 - t_7$             | $I_6 < 0$ |

| $t_7 - t_8$             | $I_7 < 0$ |

$V_{CI}$ ,  $V_{CS4}$  reaches zero and  $D_3$  starts conducting (Fig. 3(d)). Therefore,  $S_4$  can be turned on at any time during *interval* 5 at ZVS. It is important to note that the main condition for  $S_1$  to turn off at quasi-ZCS and  $S_4$  to turn on at ZVS is positive transformer current. Then, in Fig. 2 at  $t_3$ ,  $I_3$  must also be positive to allow the soft-switching operation to happen.

From Fig. 2, if the constraints  $I_0 < 0$  and  $I_1 > 0$  are met and the converter is operating in buck mode (0 < m < 1), then the next constrains  $I_2 > 0$  and  $I_3 > 0$  are also going to be satisfied because the transformer current will have a positive slope. Therefore, the only soft-switching conditions that need to be considered while operating with m < 1 are  $I_0 < 0$  and  $I_1 > 0$ , which gives the following soft-switching restrictions:

$$D_{T1} \ge \frac{2(1 - D_{T3})}{1 + 1/m},\tag{33}$$

$$D_{T2} \ge \frac{2(1 - D_{T3})}{1 + m} \,. \tag{34}$$

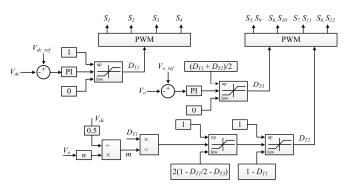

From (33) and (34) it is clear that for buck mode operation  $D_{T2} \ge D_{Tl}$ . Then, the secondary side duty cycle is chosen to be equal to  $D_{T2} = D_{Tl}/m$ . Fig. 9 presents the implemented control scheme. The PI controller implemented to control the dc bus voltage  $V_{dc}$  was designed to be 10 times slower than the one to control the output voltage  $V_o$ .

### IV. DESIGN PROCEDURE AND EXAMPLE

### A. Specifications

The input voltage is defined to be 120 Vrms, the rated output power 500 W, the output voltage is 48 Vdc and the system was designed to operate at an arbitrary switching frequency of 20 kHz.

Fig. 8. Equivalent circuits for the transition from *interval 3*  $[t_2 - t_3]$  to *interval 4*  $[t_3 - t_4]$ .

Fig. 9. Implemented control scheme for the new boost SST topology.

### B. Number of Series Connected Modules and Intermediate Bus Voltage

The intermediate dc bus voltage is selected to be 400 Vdc, so  $g = 400/120\sqrt{2} = 2.35$ . According to Fig. 5, g could have been chosen larger, e.g. g = 3 to achieve a larger PF; however, this requires a larger dc bus voltage, which would have impacted in the isolation and size of some components. The number of cascaded modules  $N_m$  is selected to be 1.

### C. Operating Range for $D_{TI}$

Based on (20), the operating range of  $D_{TI}$  is defined as:  $0.1489 < D_{TI} < 1$ .

### D. Total and per Module Bus Voltage ( $V_{dc(total)}$ and $V_{dc}$ )

$$V_{dc(total)} = 120\sqrt{2}g = 400 \text{ V},$$

$$V_{dc} = \frac{V_{dc(total)}}{N_m} = 400 \text{ V}.$$

E. Voltage Rating of the Capacitors  $C_1$  and  $C_2$ , Primary Side Devices  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ , Front End Diodes  $D_1$  and  $D_2$  and Three-Level Bridge Diodes  $D_3$  and  $D_4$

$$V_{C1}, V_{C2} > \frac{V_{bus(total)}}{2N_m} = 200 \text{ V},$$

$$V_{D1}, V_{D2} > \frac{V_{bus(total)}}{N_m} = 400 \text{ V},$$

$$V_{S1}, V_{S2}, V_{S3}, V_{S4} > V_{C1} = 200 \text{ V},$$

$$V_{D3}, V_{D4} > V_{C1} = 200 \text{ V}.$$

### F. Boost Inductor Design

From (21), the maximum boost inductor value is obtained as:  $L_b < L_{b\_critic} = 360 \mu H$ . The exact value is obtained from (27) as  $L_b = 284 \mu H$ .

### G. Transformer Design

For buck mode of operation m < 1:

Selecting m = 0.8, the turns ratio of the transformer is calculated as:

| TABLE III EXPERIMENTAL PROTOTYPE AND SPECIFICATIONS |                                                                                        |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------|--|

|                                                     |                                                                                        |  |

| Front-End Stage                                     |                                                                                        |  |

| Si Diode                                            | RURG5060_F085                                                                          |  |

| $C_1 = C_2$                                         | $V_R = 600 \text{ V}, I_D = 50 \text{ A}, V_{FM} = 1.4 \text{ V}$<br>470 $\mu\text{F}$ |  |

| ·                                                   |                                                                                        |  |

| DC-AC Three-Level Stage                             |                                                                                        |  |

| Si MOSFET                                           | AOK60N30L                                                                              |  |

|                                                     | $BV_{DSS} = 300 \text{ V}, I_D = 40 \text{ A},$                                        |  |

|                                                     | $R_{DS(ON)} = 0.056 \Omega$                                                            |  |

| SiC Diode                                           | GP2D020A060B                                                                           |  |

|                                                     | $V_R = 600 \text{ V}, I_D = 31 \text{ A}, V_{FM} = 2 \text{ V}$                        |  |

| $C_d$                                               | 1 μF                                                                                   |  |

| AC-DC Stage                                         |                                                                                        |  |

|                                                     | RFP4310ZPBF                                                                            |  |

| Si MOSFET                                           | $BV_{DSS} = 100 \text{ V}, I_D = 95 \text{ A},$                                        |  |

|                                                     | $R_{DS(ON)} = 6 \text{ m}\Omega$                                                       |  |

| $C_o$                                               | 3900 μF                                                                                |  |

| HF-XFMR                                             |                                                                                        |  |

| Power Rating                                        | 2 kVA                                                                                  |  |

| Voltage Ratio                                       | 35/9 (two secondary windings)                                                          |  |

| Fundamental Frequency                               | 20 kHz                                                                                 |  |

| Optimum Flux Density                                | 0.24 T                                                                                 |  |

| Leakage Inductance                                  | 0.5 mH                                                                                 |  |

| Core Material                                       | Amorphous, Metglas® 2605SA1,                                                           |  |

TARIFIII

$$n = \frac{mV_C}{V_o} = 2.39$$

.

AMCC-50

259/36 served Litz wire

The leakage inductance is designed from the transfer power equation (28) for maximum power transmission conditions  $D_{TI} = 1$ ,  $D_{T2} = 1$  and  $D_{T3} = 0.5$ :

$$P = \frac{2}{T_{sw}} \int_{0}^{T_{sw}/2} v_{p}(t) i_{p}(t) dt = \frac{V_{C} n V_{o}}{8 f_{sw} L_{k}}.$$

Then, the leakage inductance is obtained as:

Wire

$$L_{lk} < \frac{V_C n V_o}{8 f_{sw} P_{in}} = 285.9 \, \mu \text{H}.$$

### H. Current Rating of the Switching Devices

Evaluating the equations from Table I, the current rating of the devices can be obtained.

### V. EXPERIMENTAL RESULTS

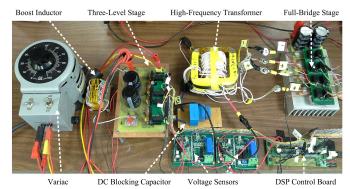

To validate the functionality of the boost-based topology, a scaled-down version of the converter presented in Fig. 1 is prototyped and tested for different load conditions. The system comprises four stages: A front-end ac-dc stage with two 600 V/50 A Si diodes, a three-level dc-ac stage with 300 V/40 A, Si MOSFETs, a HF-XFMR and a four-leg ac-dc full-bridge converter with 100 V/95 A, Si MOSFETs. The maximum boost inductance to operate in DCM is calculated as 0.36 mH using (21). The transformer leakage inductance is set to 0.285 mH and the transformer efficiency is 98% and optimum flux density  $B_{opt}$  is approximately 0.24 T. The specifications of the topology's stages are listed in Table III.

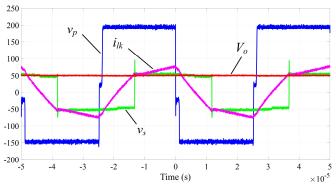

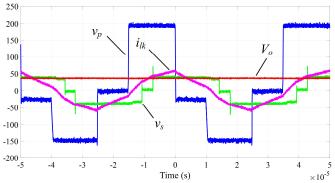

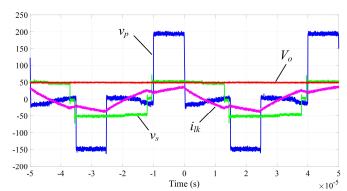

The measured transformer input and output voltages and current flowing through the leakage reactance are illustrated in Figs. 10 - 12 for 100%, 80% and 40% rated power. The

Fig. 10. Transformer primary voltage (blue) and secondary voltage (green), primary current (pink) and output voltage (red) at rated power.

Fig. 11. Transformer primary voltage (blue) and secondary voltage (green), primary current (pink) and output voltage(red) at 80% of rated power.

Fig. 12. Transformer primary voltage (blue) and secondary voltage (green), primary current (pink) and output voltage (red) at 40% of rated power.

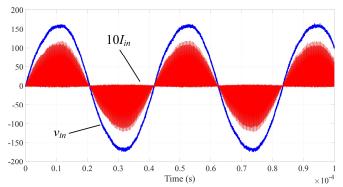

Fig. 13. Converter input voltage (blue) and input current (red).

waveforms shapes are the result of commutation scheme presented in Fig. 2. The input and output voltages were maintained at 400 Vdc and 48 Vdc, respectively. However,

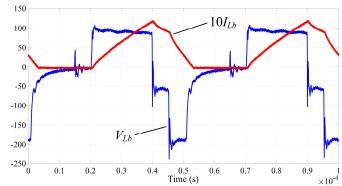

Fig. 14. Boost inductor voltage (blue) and current (red).

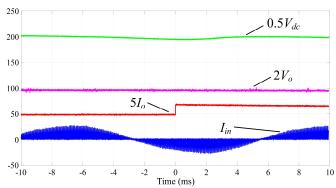

Fig. 15. DC bus voltage (green), output voltage (pink), output current (red) and input current (blue).

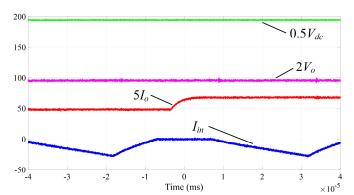

Fig. 16. Zoomed versions of the dc bus voltage (green), output voltage (pink), output current (red) and input current (blue).

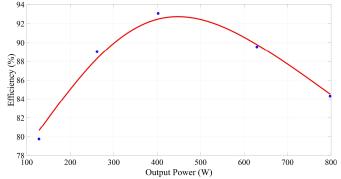

Fig. 17. Efficiency measurement.

there was a voltage imbalance between the two capacitors in the primary dc bus (see the blue waveforms). Blocking capacitor  $C_d$  was connected in series with the HF-XFMR to

Fig. 18. Photo of the experimental setup.

avoid any dc offset caused by delays and dead times. Based on the analysis done in Section III and using Table II, all requirements for soft-switching are accomplished for the power conditions shown in Figs. 10 and 11. Therefore, all the transitions are done in a lossless manner. This does not happen for all transitions of the primary side switches at low load conditions (see Fig. 12). The reason is due to the fact that the imposed soft-switching conditions interfere with voltage control requirements. At low power conditions, the controller needs to make  $D_{TI}$  and  $D_{T3}$  smaller, which forces  $D_{T2}$  to grow larger as required by the constraint in (31), resulting in a further increase of the output voltage. Therefore, a relaxation of the constraints for soft-switching is needed to control the output voltage while losing the soft-switching operation for some devices.

The boost inductor current and ac input voltage are presented in Fig. 13. The input current operates in DCM and has two negative slopes when decreasing in value. A zoomed version of the boost inductor current and voltage are shown in Fig. 14.

The dynamic response of the proposed topology under a sudden 42% increase of load condition is shown in Figs. 15 and 16. It can be seen that the output voltage remains almost constant while the voltage sag at the dc link voltage is about 5% of the rated dc link voltage. Fig. 17 presents the efficiency measurements of the proposed prototype and Fig. 18 illustrates the experimental setup used to test the prototype.

### VI. CONCLUSIONS

A new unidirectional-power-flow SST topology with reduced number of switches in the HV-side was presented. The proposed converter has four diodes and four IGBTs (operating under ZVS) in the transformer HV side, whereas the traditional bidirectional-power-flow SST based-DAB topology has eight IGBTs operating under hard switching.

The HV-side capacitor voltage is controlled using the primary side duty cycle  $D_{TI}$  and transferred power can be controlled by adjusting the fundamental phase-shift between the primary and secondary voltage waveforms,  $D_{T3}$ . Constraints were placed upon the secondary duty cycle  $D_{T2}$  to ensure the mode of operation and thus ZVS for all of the switches. In addition to this, the HF-XFMR two-winding configuration and the four-leg full-bridge converter, helps

reduce current stresses on the LV power semiconductor devices.

### REFERENCES

- [1] D.G. Shah, M.L. Crow, "Stability design criteria for distribution systems with solid-state transformers," *IEEE Transactions on Power Delivery*, vol. 29, no. 6, pp. 2588–2595, December, 2014.

- [2] J.W. Kolar, G. Ortiz, "Solid-state-transformer: Key components of future traction and smart systems," in *Proceeding of the International Power Electronics Conference*, IPEC 2014, pp. 1–14, May, 2014.

- [3] S. Xu, Y. Xunwei, F. Wang, A.Q. Huang, "Design and demonstration of 3.6 kV-120 V/10 kVA solid-state transformer for smart grid application," *IEEE Transactions on Power Electronics*, vol. 29, no. 8, pp. 3982–3988, August, 2014.

- [4] X. She, A.Q. Huang, R. Burgos, "Review of solid-state transformer technologies and their application in power distribution systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 1, no. 3, pp. 186–198, September, 2013.

- [5] X. She, R. Burgos, G. Wang, F. Wang, A.Q. Huang, "Review of solid state transformers in the distribution system: From components to field application," in *Proceedings of the IEEE Energy Conversion Congress* and Exposition, ECCE 2012, pp. 4077–4084, September, 2012.

- [6] B. Thomas, M. Akos, D. Dujic, "Power electronic traction transformer: Efficiency improvements under light-load conditions," *IEEE Transactions on Power Electronics*, vol. 29, no. 8, pp. 3971–3981, August. 2014.

- [7] X. She, X. Yu, F. Wang, A.Q. Huang, "Design and demonstration of a 3.6-kV-120-V/10-kVA solid-state transformer for smart grid application," *IEEE Transactions on Power Electronics*, vol. 29, no. 8, pp. 3982–3996, August, 2014.

- [8] S. Falcones, X. Mao, R. Ayyanar, "Topology Comparison for solid state transformer implementation," in *Proceedings of the IEEE Power and Energy Society General Meeting*, pp. 1–8, July, 2010.

- [9] R.J. Garcia Montoya, A. Mallela, J.C. Balda, "An evaluation of selected solid-state transformer topologies for electric distribution systems," in Proceedigns of the IEEE Applied Power Electronics Conference and Exposition, APEC 2015, pp. 1022–1029, March, 2015.

- [10] X. She, R. Burgos, G. Wang, F. Wang and A. Q. Huang, "Review of solid state transformer in the distribution system: From components to field application," 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, 2012, pp. 4077-4084.

- [11] B. Zhao, S. Qiang, W. Liu, Y. Sun, "Overview of dual-active-bridge isolated bidirectional DC-DC converter for high-frequency-link powerconversion system," *IEEE Transactions on Power Electronics*, vol. 29, no. 8, pp. 4091–4106, August, 2014.

- [12] G.G. Oggier, G.O. Garcia, A. Oliva, "Switching control strategy to minimize dual active bridge converter losses," *IEEE Transaction on Power Electronics*, vol. 24, no. 7, pp. 1826–1838, July, 2009.

- [13] T. Zhao, G. Wang, S. Bhattacharya, A.Q. Huang, "Voltage and power balance control for a cascaded H-bridge converter-based solid-state transformer," *IEEE Transactions on Power Electronics*, vol. 28, no. 4, pp. 1523–1532, April, 2013.

- [14] T. Zhao, G. Wang, J. Zeng, S. Dutta, S. Bhattacharya, A.Q. Huang, "Voltage and power balance control for a cascaded multilevel solid state transformer," in *Proceedings of the 25<sup>th</sup> IEEE Applied Power Electronics Conference and Exposition*, APEC 2010, pp. 761–767, February, 2010.

- [15] D. Rothmund, G. Ortiz and J. W. Kolar, "SiC-based unidirectional solid-state transformer concepts for directly interfacing 400V DC to Medium-Voltage AC distribution systems," 2014 IEEE 36th International Telecommunications Energy Conference (INTELEC), Vancouver, BC, 2014, pp. 1-9.

- [16] F. Krismer, J. W. Kolar, "Efficiency-Optimized High-Current Dual Active Bridge Converter for Automotive Applications", *IEEE Trans. on Industrial Electronics*, Vol. 59, No. 7, July 2012.

- [17] Y. Choi, "A Highly Power-Efficient LED Back-Light Power Supply for LCD Display," *Journal of Display Technology*, Vol. 9, no. 5, pp. 383-384, May 2013.

- [18] Y. Choi, Y. Song, L. Jason, "A Novel Bridgeless Single-Stage Half-Bridge AC/DC Converter," Applied Power Electronics Conference and Exposition (APEC), 2010 25th Annual IEEE, pp. 42-46, Feb 2010.

- [19] P.M. Barbosa, F. Canales, J.M. Burdío, F.C. Lee, "A three-level converter and its applications to power factor correction," *IEEE Transactions on Power Electronics*, vol. 20, no. 6, pp. 1319–1327, November, 2005.

- [20] L. A. Garcia-Rodriguez, J. C. Balda, A. Mallela and A. Escobar-Mejía, "A new SST topology comprising boost three-level AC/DC converters for applications in electric power distribution systems," 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, 2015, pp. 6051-6058.

- [21] S. Dusmez, X. Li and B. Akin, "A Fully Integrated Three-Level Isolated Single-Stage PFC Converter," in *IEEE Transactions on Power Electronics*, vol. 30, no. 4, pp. 2050-2062, April 2015.

- [22] K. H. Liu and Y. L. Lin, "Current waveform distortion in power factor correction circuits employing discontinuous-mode boost converters," *Power Electronics Specialists Conference*, 1989. PESC '89 Record., 20th Annual IEEE, Milwaukee, WI, 1989, pp. 825-829 vol.2.

- [23] A. Medury, J. Carr, J.C. Balda, A.H Mantooth, T. Funaki, "Three-level ZVZCS and ZVS half-bridge converters: A comparative evaluation," in Proceedings of the IEEE Power Conversion Conference, PCC 2007, pp. 892–898, April, 2007.

- [24] J. Huang, Y. Wang, Z. Li and W. Lei, "Unified Triple-Phase-Shift Control to Minimize Current Stress and Achieve Full Soft-Switching of Isolated Bidirectional DC–DC Converter," in *IEEE Transactions on Industrial Electronics*, vol. 63, no. 7, pp. 4169-4179, July 2016.

- [25] A. K. Jain and R. Ayyanar, "Pwm control of dual active bridge: Comprehensive analysis and experimental verification," in *IEEE Transactions on Power Electronics*, vol. 26, no. 4, pp. 1215-1227, April 2011.

- [26] IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems," in *IEEE Std 519-2014 (Revision of IEEE Std 519-1992)*, vol., no., pp.1-29, June 11 2014.

Luciano Andres Garcia Rodriguez (S'12) received his B.S degree in electronics engineering from the Universidad Nacional del Sur (UNS) in Bahía Blanca, Argentina. In 2012, he joined the Sustainable Smart Electric Energy Systems (SSEES) laboratory at the University of Arkansas where he is working toward a Ph.D. degree. His

research interests include power electronics, converter typologies and control systems.

Vinson Jones (S'16) received both his B.S. and M.S. in Electrical Engineering from University of Arkansas, Fayetteville, AR, USA in 2014 and 2016 respectively. Currently, he is a doctoral student in the Department of Electrical Engineering at the University of Arkansas, Fayetteville, AR, USA. His research interests include grid connected power electronics and

power quality.

Alejandro Raúl Oliva received the B.S.E.E. degree from the Universidad Nacional del Sur (UNS), Bahía Blanca, Argentina, in 1987, and the M.S. and Ph.D. degrees in electrical engineering from the University of Arkansas, Fayetteville, AR, USA, in 1996 and 2004, respectively.

management.

He has been a Professor in the Electrical Engineering Department of the UNS since 1999, and member of the Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET), Buenos Aires, Argentina, since 2005. He has published a book and more than 50 journals and proceedings. His main research interests are power electronics and power

Andrés Escobar-Mejía (S'09–M'15) received the B.E. degree and the M.Sc. degree both in electrical engineering from La Universidad Tecnológica de Pereira, Risaralda, Colombia, in 2002 and 2004, respectively. He got his Ph.D. degree at the University of Arkansas, Fayetteville, AR, USA, under Dr. J. C. Balda advisory in 2014.

In 2007, he joined the Department of Electrical Engineering, at La Universidad Tecnológica de Pereira, as a Lecturer, and became an Associate Professor in 2014. For the past seven years, he has been working on the area of power electronics with emphasis on matrix converters, dc-dc isolated converters and the integration of renewables with the power grid. He is also working on electrical machines and drives, active filters, flexible ac transmission systems, high-voltage dc, and power quality.

(M'78-SM'94)Juan Carlos Balda received B.Sc. Electrical his in Universidad Engineering from the Nacional del Sur (Bahía Blanca, Argentina) in 1979. He received his Ph.D. degree in Electrical Engineering from the University of Natal (Durban, South Africa) in 1986. He was then employed as a researcher and a part-time lecturer at

the University of Natal until July 1987. He then spent two years as a visiting Assistant Professor at Clemson University, South Carolina. He has been at the University of Arkansas at Fayetteville since July 1989 where he is currently a University Professor, Department Head, associate director for applications of the National Center for Reliable Electric Power Transmission (NCREPT) and campus director for the NSF IUCRC Grid-connected Advanced Power Electronic Systems (GRAPES). His main research interests are Power Electronics, Electric Power Distribution Systems, Motor Drives and Electric Power Quality. He is a senior member of the IEEE, member of the Power Electronics and Power & Energy Societies, and the honor society Eta Kappa Nu. He is also a vice-chair of IEEE PELS TC5 committee and faculty advisor to the local chapter of the IEEE Power Electronics Society.