# Control System to Balance Internal Currents of a Multilevel Current-Source Inverter

Pablo Cossutta, *Member*, *IEEE*, Miguel Pablo Aguirre, *Senior Member*, *IEEE*, Mathias Angelico Engelhardt, *Member*, *IEEE* and María Inés Valla, *Fellow Member*, *IEEE*

Abstract—Multilevel Current Source Inverters (MCSI) have proved to be a high performance option for industrial applications due to reliability, fault tolerant capabilities, quasi soft switching and the use of lower filter capacitor values. One of its major challenges is to balance the internal currents that feed each module. Imbalances could be caused by manufacturing deviations of the reactive components, temperature drift or aging, nonlinear loads and modulation errors, among others. Using the well-known Phase Shift Carrier Sinusoidal Pulse Width Modulation (PSC-SPWM), a slight change in the amplitude of the carrier signals produces a variation in the average value of the internal currents. In this paper, we introduce a control strategy to balance the current of the inductors and its implementation in a prototype. Simulation and experimental results at different operating conditions show a robust behavior of the control system along with a low distortion in the output voltages and currents of the converter.

Index Terms—Multilevel Current Source Inverter; FPGA Control; Inductor Current Balance.

#### I. Introduction

VER the past years, multilevel power converters have been used in several applications such as battery chargers [1], power factor correctors [2] and active filters [3], motor control [4]–[6] and interface with alternative energy sources [7]–[9], among many others [10]. They can be implemented both as a Multilevel Voltage Source Inverter (MVSI) or Multilevel Current Source Inverter (MCSI).

MCSIs particularly offer a great number of advantages such as a fast dynamic response, fault tolerant capabilities and the reduction of high frequency electrical disturbances in the load. Furthermore, they have less current stress in the switches and an increased Medium Time Between Failures (MTBF) because of the higher reliability of inductors compared to MVSI capacitors [11]–[13]. Their main disadvantages are the required reverse voltage blocking capabilities of the switches,

Manuscript received January 3, 2017; revised April 4, 2017, May 24, 2017; accepted Jul 20, 2017. This work was supported by the Instituto Tecnológico de Buenos Aires (ITBA), Universidad Nacional de La Plata (UNLP), Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET) and Agencia Nacional de Promoción de Ciencia y Tecnología (ANPCyT) through grants PICT-2015-3040, PIP-2015-0100496 and UNLP-11/I217, Argentina.

Pablo Cossutta, Miguel Pablo Aguirre, Mathias Angelico Engelhardt are with Centro de Investigación y Desarrollo en Electrónica Industrial (CIDEI), ITBA, Buenos Aires, Argentina (e-mail: pcossutt@itba.edu.ar).

María Inés Valla is with Instituto de Investigaciones en Electrónica, Control y Procesamiento de Señales (LEICI, CONICET-UNLP) Facultad de Ingeniería, UNLP, La Plata, Argentina.

and the size and weight of the internal inductors. These disadvantages could be partially solved by using wide band gap devices such as SiC and GaN that allows to increase the frequency without affecting efficiency [14]–[16].

The topology called "Single Rating Inductor MCSI" in [17] consists of n identical Current Source Inverter (CSI) modules. Each module is composed of two balance inductors and six switches that have reverse voltage blocking characteristics. One of the modulation techniques commonly used in these kind of converters is the well-known Phase Shift Carrier Sinusoidal Pulse Width Modulation (PSC-SPWM) [18], [19], which is based on the comparison of three sinusoidal references with a triangular carrier. Each module applies the SPWM technique taking into account that the phase of the carrier must be equally shifted by  $\frac{360}{n}$  degrees.

The MCSI presents 2n+1 current levels since each module

The MCSI presents 2n+1 current levels since each module has the capability of injecting  $\pm \frac{1}{n}$  of the main DC current. The whole operation of the MCSI assumes that each module have the same current value. However, unmatched components, unequal ON-state characteristics of the semiconductor devices, modulation errors and nonlinear loads could cause an imbalance in these currents, so a balancing method must be implemented.

Even though the issue related to the voltage imbalance in the capacitors of different MVSI topologies has been widely studied in the literature [20]–[24], only a few techniques applied to the MCSI topology could be found [25]–[28].

The methods proposed in [25] and [26] deal with a 5-level MCSI and they are not easily extended to more levels. In [25] the balance of the internal currents is achieved by choosing the proper redundant vector in the Space Vector Modulation (SVM). In [26] a complex logic is used to modify the PSC-SPWM in order to balance the current of the two modules. Extra hardware is introduced in [27] to balance the currents in a 5-level single phase MCSI. Two methods based on the PSC-SPWM were proposed in [28]. A slight change either in the amplitude or the phase of the triangular carriers causes a change in the internal currents that could be used to generate a balanced operating point. The controller action slightly affects the output current THD without affecting the switching losses.

In this paper, the mathematical model of the MCSI and a current balance control algorithm is developed. A new version of the algorithm proposed in [28] is presented, analyzed and verified with an MCSI prototype under different experimental conditions. The proposed controller is based on controlling the average value between the upper and lower currents of

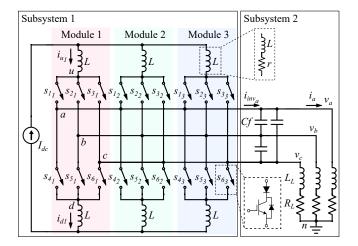

Fig. 1. MCSI Topology

each CSI module. The controller, along with the SPWM, are implemented in a Field Programmable Gate Array (FPGA) as in [29], allowing high speed data processing, variable bit accuracy, fault tolerant architectures and easily scalable design [30], [31]. In addition to these qualities, one of the most powerful advantages of an FPGA is the ability to compute all the converter control blocks in parallel, saving time and increasing reliability. In order to be scalable and comparable to the experimental results, simulation models in this paper consider the internal logic timing, the switches behavior, the parameters of the experimental setup, and the saturation limits of the actual control system.

In detail, this paper is organized as follows: in Section II, the system is described and its mathematical model is obtained. Then, the modulator and proposed controller are shown. Section III presents and analyzes the simulation results. Experimental results are shown in Section IV. Finally, in Section V some conclusions are drawn.

#### II. SYSTEM DESCRIPTION

The system is composed of an MCSI, a DC current source, custom acquisition boards used to measure the internal currents of the MCSI, an FPGA, filtering capacitors and the load.

## A. MCSI Topology

Fig. 1 shows the schematics of the MCSI. It consists of three Current Source Inverters (CSI) modules in parallel with a maximum of 7 different output current levels. Two inductors are required in each module to balance its current value. All the balance inductors should be identical and should carry the same average current, simplifying the design of the inverter. Each module is composed of six reverse blocking switches that could be implemented with integrated gate commutated thyristors (IGCT), reverse blocking insulated gate bipolar transistors (RB-IGBT) or insulated gate bipolar transistors (IGBT) with a series diode to block the reverse current and voltage, among others. In order to filter and improve the current and voltage waveforms at the load, a three phase capacitor of low capacitance value is placed at the output of the MCSI.

#### B. Mathematical Model

At any given time, each module of the multilevel inverter must grant a current path so one upper switch and one lower switch must be conducting. Furthermore, only one of the upper and lower devices must be conducting to ensure that the injected current of the inverter is defined only by the DC current source and the state of the switches. These restrictions can be stated as follows

$$s_{1_y} + s_{2_y} + s_{3_y} = s_{4_y} + s_{5_y} + s_{6_y} = 1 \quad y \in \{1, 2, 3\}$$

(1)

Where the last sub index y is the module number, with  $s_{1,6_y}=1$  when the switch is conducting and 0 otherwise. The proposed topology can be modeled as two interconnected subsystems: one involving the MCSI with its current source and other composed of filtering capacitors and a load, which are shown in Fig. 1 as Subsystem 1 and Subsystem 2. Both models have 6 state variables with the output of the first model connected to the input of the second one and vice versa. Applying the Kirchhoff's laws on the topology and rearranging the equations, the space state model of the MCSI is obtained

$$\begin{bmatrix} i_{u_{1}} \\ i_{u_{2}} \\ i_{u_{3}} \end{bmatrix} = \frac{1}{3L} \Gamma \begin{bmatrix} v_{un_{1}} \\ v_{un_{2}} \\ v_{un_{3}} \end{bmatrix} - \frac{r}{L} \begin{bmatrix} i_{u_{1}} \\ i_{u_{2}} \\ i_{u_{3}} \end{bmatrix} + \frac{r}{3L} \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix} I_{dc}$$

$$\begin{bmatrix} i_{d_{1}} \\ i_{d_{2}} \\ i_{d_{3}} \end{bmatrix} = \frac{1}{3L} \Gamma \begin{bmatrix} v_{nd_{1}} \\ v_{nd_{2}} \\ v_{nd_{3}} \end{bmatrix} - \frac{r}{L} \begin{bmatrix} i_{d_{1}} \\ i_{d_{2}} \\ i_{d_{3}} \end{bmatrix} + \frac{r}{3L} \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix} I_{dc}$$

(2)

where L is the self inductance of each module with an internal resistance r, the matrix  $\Gamma$  is

$$\Gamma = \begin{bmatrix} -2 & 1 & 1\\ 1 & -2 & 1\\ 1 & 1 & -2 \end{bmatrix} \tag{3}$$

and

$$\begin{bmatrix} v_{un_1} \\ v_{un_2} \\ v_{un_3} \end{bmatrix} = \begin{bmatrix} s_{1_1} & s_{2_1} & s_{3_1} \\ s_{1_2} & s_{2_2} & s_{3_2} \\ s_{1_3} & s_{2_3} & s_{3_3} \end{bmatrix} \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix}$$

$$\begin{bmatrix} v_{nd_1} \\ v_{nd_2} \\ v_{nd_3} \end{bmatrix} = -\begin{bmatrix} s_{4_1} & s_{5_1} & s_{6_1} \\ s_{4_2} & s_{5_2} & s_{6_2} \\ s_{4_3} & s_{5_3} & s_{6_3} \end{bmatrix} \begin{bmatrix} v_a \\ v_b \\ v_c \end{bmatrix}$$

$$(4)$$

in which  $s_{x_y}$  are the state of the switches, x is the switch number and y is the module number. The output current of the inverter is stated as follows

$$\begin{bmatrix} i_{inv_a} \\ i_{inv_b} \\ i_{inv_c} \end{bmatrix} = \begin{bmatrix} s_{1_1} & s_{1_2} & s_{1_3} \\ s_{2_1} & s_{2_2} & s_{2_3} \\ s_{3_1} & s_{3_2} & s_{3_3} \end{bmatrix} \begin{bmatrix} i_{u_1} \\ i_{u_2} \\ i_{u_3} \end{bmatrix} - \begin{bmatrix} s_{4_1} & s_{4_2} & s_{4_3} \\ s_{5_1} & s_{5_2} & s_{5_3} \\ s_{6_1} & s_{6_2} & s_{6_3} \end{bmatrix} \begin{bmatrix} i_{d_1} \\ i_{d_2} \\ i_{d_3} \end{bmatrix}$$

(5)

The second subsystem that includes the load and the filter capacitors is modeled by

$$\begin{bmatrix} \dot{v}_{a} \\ \dot{v}_{b} \\ \dot{v}_{c} \\ \dot{i}_{a} \\ \dot{i}_{b} \\ \dot{i}_{c} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & a & 0 & 0 \\ 0 & 0 & 0 & 0 & a & 0 \\ 0 & 0 & 0 & 0 & 0 & a \\ 0 & 0 & 0 & c & 0 & 0 \\ 0 & b & 0 & 0 & c & 0 \\ 0 & 0 & b & 0 & 0 & c \end{bmatrix} \begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \\ i_{a} \\ i_{b} \\ i_{c} \end{bmatrix} - a \begin{bmatrix} i_{inv_{a}} \\ i_{inv_{b}} \\ i_{inv_{c}} \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

$$a = -\frac{1}{3 C_{f}} \qquad b = \frac{1}{L_{L}} \qquad c = -\frac{R_{L}}{L_{L}}$$

$$(6)$$

Where  $C_F$  represents the filter capacitance,  $R_L$  the load resistance and  $L_L$  load inductance. The interconnection between the two subsystems can be seen in (4) and (5). As shown in (2), the dynamics of the upper and lower currents,  $i_{u_y}$  and  $i_{d_y}$ , are different because they depend on the state of the switches and load voltages. Thus, a classic controller would have taken into account the values of the six internal currents in order to balance them. However, balancing the average value between the upper and lower currents for each module is a simpler approach that produces similar results. The average currents are defined by

$$\bar{i_y} = \frac{i_{u_y} + i_{d_y}}{2} \quad y \in \{1, 2, 3\}$$

(7)

As this paper is focused on balancing the average currents, the resulting dynamics to control can be expressed as

$$\begin{bmatrix} \bar{i}_1 \\ \bar{i}_2 \\ \bar{i}_3 \end{bmatrix} = \frac{1}{6L} \begin{bmatrix} -2 & 1 & 1 \\ 1 & -2 & 1 \\ 1 & 1 & -2 \end{bmatrix} \begin{bmatrix} v_1 \\ v_2 \\ v_3 \end{bmatrix} - \frac{r}{L} \begin{bmatrix} \bar{i}_1 \\ \bar{i}_2 \\ \bar{i}_3 \end{bmatrix} + \frac{r}{3L} \begin{bmatrix} 1 \\ 1 \\ 1 \end{bmatrix} I_{dc}$$

(8)

Where the equivalent voltages of each module,  $v_1$ ,  $v_2$  and  $v_3$  are defined by

$$\begin{bmatrix} v_1 \\ v_2 \\ v_3 \end{bmatrix} = \begin{bmatrix} v_{un_1} \\ v_{un_2} \\ v_{un_3} \end{bmatrix} + \begin{bmatrix} v_{nd_1} \\ v_{nd_2} \\ v_{nd_3} \end{bmatrix}$$

(9)

Since  $v_{1,2,3}$ , in (8), depend on the state of the switches, a variation in the modulation algorithm could be used to produce a change in the average current of all the modules.

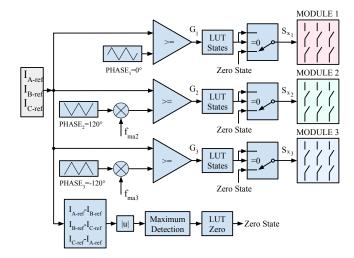

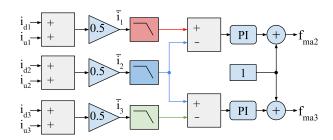

# C. Modulation

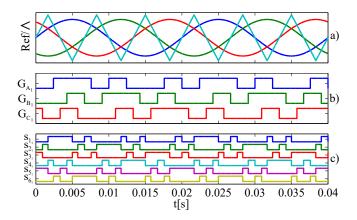

The modulation of the MCSI is performed applying the Phase Shift Carrier Sinusoidal Pulse Width Modulation (PSC-SPWM). It is based on comparing the reference sinusoidal signals with three equally phase-shifted triangular carriers [18]. A block diagram of the modulation stage is presented in Fig. 2, where  $f_{ma2,3}$  are the outputs of the controller which is described in the next section. They are equal to 1 when the control is disabled. The implementation of this modulation in a CSI is not as simple as in a VSI since it requires more logic manipulation to generate the desired current levels at the output while ensuring a current path in all the inductors. Since the modulation algorithm is similar for each module, the modulation scheme of the first one is used as an example. The different signals of the modulation process are shown in Fig. 3. First, the current references of the MCSI,  $I_{A-ref}$   $I_{B-ref}$  and

Fig. 2. Modulation Scheme

Fig. 3. SPWM Detail of one module

TABLE I LUT STATES OF MODULE x

| Input     |           |           | Output    |           |           |           |           |           |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| $G_{A_x}$ | $G_{B_x}$ | $G_{C_x}$ | $s_{1_x}$ | $s_{2_x}$ | $s_{3_x}$ | $s_{4_x}$ | $s_{5_x}$ | $s_{6_x}$ |

| 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

| 0         | 0         | 1         | 0         | 0         | 1         | 0         | 1         | 0         |

| 0         | 1         | 0         | 0         | 1         | 0         | 1         | 0         | 0         |

| 0         | 1         | 1         | 0         | 0         | 1         | 1         | 0         | 0         |

| 1         | 0         | 0         | 1         | 0         | 0         | 0         | 0         | 1         |

| 1         | 0         | 1         | 1         | 0         | 0         | 0         | 1         | 0         |

| 1         | 1         | 0         | 0         | 1         | 0         | 0         | 0         | 1         |

| 1         | 1         | 1         | 0         | 0         | 0         | 0         | 0         | 0         |

| 1         |           | •         |           |           |           |           |           |           |

$I_{C-ref}$  are compared with the triangular carrier as depicted in Fig. 3a. The standard VSI SPWM signals  $G_{A_1}$ ,  $G_{B_1}$  and  $G_{C_1}$ , shown in Fig. 3b are generated by the comparators. They are used as inputs of the Look Up Table States (LUT States), as shown in the top part of Fig. 2. The LUT States, shown in Table I, are used to transform the active vectors of a VSI, generated by the SPWM, into equivalent active vectors of a CSI. Zero vectors are considered separately. Since each module can produce a zero current state by turning

$\begin{array}{c} \text{TABLE II} \\ \text{LUT ZERO, } x = 1, 2, 3 \end{array}$

| Maximum                              | Output    |           |           |           |           |           |

|--------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| value                                | $s_{1_x}$ | $s_{2_x}$ | $s_{3_x}$ | $s_{4_x}$ | $s_{5_x}$ | $s_{6_x}$ |

| $I_{A-ref} - I_{B-ref}$              | 1         | 0         | 0         | 1         | 0         | 0         |

| $\left I_{B-ref}-I_{C-ref}\right $   | 0         | 1         | 0         | 0         | 1         | 0         |

| $\left I_{C-ref} - I_{A-ref}\right $ | 0         | 0         | 1         | 0         | 0         | 1         |

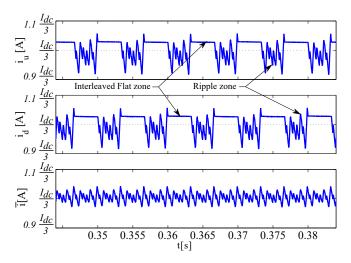

Fig. 4. From top to bottom. First trace:  $i_u$ , second trace  $i_d$ , and third trace:  $\bar{i}_t$ , average current of one module

on both switches in any of its three legs, the CSI has one extra zero state than the VSI. This extra redundancy could be used to reduce the commutation frequency, reduce the power dissipation and increase the efficiency. To select the zero state that meets these goals, first three current differences are calculated and the one that gets the maximum absolute value is related with the optimum zero state. Another look up table (LUT Zero), which is shown in Table II, holds the zero states. Both the output of the LUT States and the LUT Zero are fed into a multiplexer. The outputs of the multiplexer,  $s_{1_1}$ ,  $s_{2_1}$ ,  $s_{3_1}$ ,  $s_{4_1}$ ,  $s_{5_1}$  and  $s_{6_1}$  are shown in Fig. 3c.

## D. Controller

One of the major drawbacks of the multilevel topologies is that the average currents of each module,  $\bar{i}_{1,2,3}$ , may have different mean values. This could be caused by nonlinear loads, imperfections of the modulation algorithm, unequal ON-state characteristics of the semiconductor devices and component variations. In this section a control algorithm to balance these currents is presented. The control algorithm is based on one proposed in [28], which uses slight changes of the PSC-SPWM carriers. In [28], the amplitudes of the triangular carriers in the modules 2 and 3 are modified, in order to balance the internal currents. The objective of this controller is just to balance only the average between the upper,  $i_{u_y}$ , and lower,  $i_{d_y}$ , currents of each module. The upper and lower currents of one module, along with their average value are depicted in Fig. 4. It can be noticed that the current waveforms have

Fig. 5. Proposed current balance controller

two different parts: a flat zone and a ripple zone. The different mean values can be clearly recognized since the constant flat zone of each current is at a different level and depends on the relative phase and the amplitude relation between the carriers and the reference signals,  $m_a$ . The average current, defined in (7), has a lower ripple and its mean value could be obtained with a low pass filter. From (4), it can be deduced that a change in the SPWM carriers causes a change in the switch signals and hence, a change in the upper and lower voltages seen by each of the modules  $v_{un1}$ ,  $v_{un2}$ ,  $v_{un3}$ ,  $v_{nd1}$ ,  $v_{nd2}$  and  $v_{nd3}$ . Taking into account (9), these voltages are the inputs of the dynamic expressed in (8), which is the state space representation of the average currents, that must be controlled. The overall control algorithm is depicted in Fig. 5. The controller is implemented with two simple Proportional and Integral (PI) controllers. A change in the amplitude of the carrier that is used in the second module produces a variation of  $\bar{i}_1$  and  $\bar{i}_2$  while changing the amplitude of the third carrier produces a variation of  $\bar{i}_2$  and  $\bar{i}_3$ . Considering this behavior, the error signal for the first PI is implemented by the difference between  $\bar{i}_1$  and  $\bar{i}_2$  while the error signal for the second one is done by the difference between  $\bar{i}_2$  and  $\bar{i}_3$ . The low pass filter is needed because the main objective is to control the average current on the inductors of the converter and the commutation frequency must be rejected for this purpose. Since the aim of the controller is to introduce a slight change in the carrier amplitudes, a saturation of  $\pm 6\%$  of the maximum  $m_a$ , is applied to the output of the PI controllers in order to limit their action and its effect over the SPWM signals. Then, the PI outputs are added to 1 to create a scale factor for the amplitude of both carriers. Both  $f_{ma2}$  and  $f_{ma3}$  signals are fed into the modulation scheme shown in Fig. 2. The frequency of the triangular carriers is not affected as the controller changes only their amplitudes. Therefore, there is no change on the average commutation frequency and hence switching losses are not affected.

## III. SIMULATION RESULTS

Extensive simulations were performed using the SimPowerSystem toolbox from MATLAB<sup>TM</sup>/Simulink<sup>TM</sup> down to switch level. The parameters used in the simulations and experiments are shown in Table III. The chosen bandwidth for the low pass digital filter, which is used to smooth the average of the upper and lower currents of each module, is 155Hz and the modulation index ma is 0.9. The controller is designed in discrete time with a sampling time  $T_s = 1\mu s$ .

#### TABLE III System Parameters

| Parameter                          | Value              |  |  |

|------------------------------------|--------------------|--|--|

| $I_{dc}$                           | 10A                |  |  |

| Line frequency                     | 50Hz               |  |  |

| Balance inductors $(L, r)$         | $80mH, 0.75\Omega$ |  |  |

| Capacitor Filter $(C_f)$           | $4.7\mu F$         |  |  |

| Frequency Modulation Index $(m_f)$ | 21                 |  |  |

| Carrier frequency                  | 1050Hz             |  |  |

| Load $(R_L, L_L)$                  | $16\Omega, 9mH$    |  |  |

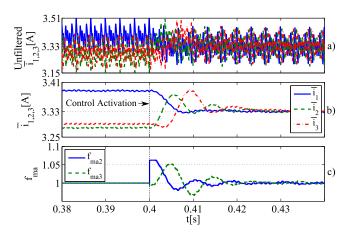

Fig. 6. Simulation of the proposed controller - Internal average currents  $ar{i}_{1,2,3}$ , filtered and unfiltered and control output signals  $f_{ma2}$  and  $f_{ma3}$

Fig. 6 shows the response of the system before and after the controller is enabled. With the controller disabled, the scale factors remains at 1 and the internal currents have a difference of 100mA. At time t=0.4s the controller is enabled and the average currents converge to approximately 3.33A in less than 30ms. The filtered average currents  $\bar{i}_{1,2,3}$  shown in Fig. 6b are used to feed the digital controllers. The output control signals that modifies the amplitude of the triangular carriers in the modulation block are depicted in Fig. 6c.

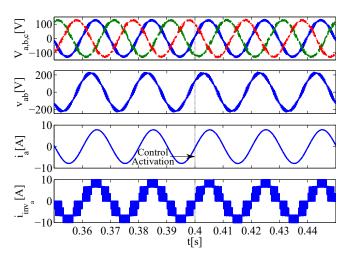

Fig. 7 shows the output variables of the system under examination. The output current  $i_a$ , shown in the third trace, is the inverter output of the phase a,  $i_{inv_a}$ , filtered by the output capacitors. The output variables of the system remain practically unchanged when the control is enabled. The output line voltage  $v_{ab}$ , shown in the second trace, is affected mainly by the fifth and higher order harmonics.

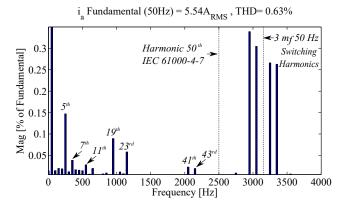

As shown in Fig. 8 the output current  $i_a$  presents low harmonic distortion and a THD of 0.63% even when the controller is enabled. The main difference with the theoretical spectrum of a discrete time SPWM modulator is the presence of low order harmonics, less than 0.025% of the fundamental current. These low order harmonics are caused by the effects of the quantization in the modulation and control algorithm. The main components of the  $i_a$  spectrum are also caused by the fifth harmonic and the switching harmonics. Since the MCSI consists of three identical modules to produce seven levels in the output current, the switching components are three

Fig. 7. Simulation of the proposed controller. Phase voltages  $v_{a,b,c}$ , line voltage  $v_{ab}$ , current  $i_a$  and the unfiltered output of the inverter  $i_{in}v_a$

Fig. 8. THD of the simulated output current  $i_a$  with the controller enabled

times the commutation frequency of the switches or  $3\,m_f\,50$  Hz, where  $m_f$  is the frequency modulation index . Hence, the harmonics corresponding to the switching frequency are centered at 3150Hz.

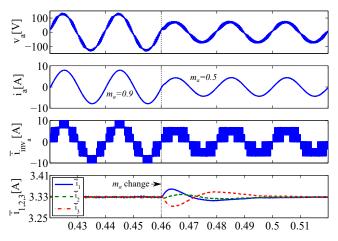

Fig. 9 shows the response of the system under a step down in  $m_a$ . At time t=0.46s it is changed from 0.9 to 0.5 and the controller is able to balance the internal currents with a settling time of less than 40ms. The change of  $m_a$  causes a reduction in the number of levels that the MCSI outputs. It also produces an instant change on the current and voltage at the load. The ripple introduced in the internal average currents during the transient is less than 2.5%.

### IV. EXPERIMENTAL RESULTS

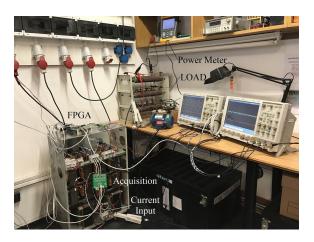

A custom acquisition system was designed and developed in order to measure the internal currents of the MCSI. The current is sensed using the ACS714 hall effect sensor, a four channel 12 bit ADC with a Serial Peripheral Interface (SPI) capable of sampling up to 1MSps, digital isolators and LVDS converters to improve the CMRR of the communication with the FPGA [32]. Control algorithms along with the SPWM and support logic are implemented on a Xilinx FPGA, Xilinx Zynq-7000 AP SoC XC7Z020. It uses 1763 LUT (look up tables), 4 digital signal processing (DSP) blocks used as multipliers in PIs, and

Fig. 9. Simulation of the proposed controller with  $m_a=0.5$ , Phase voltage  $v_a$ , phase current  $i_a$ , unfiltered output of the inverter  $i_{inv_a}$  and internal average currents  $\overline{i}_{1,2,3}$

Fig. 10. Experimental Setup

5 Block Random Access Memory (BRAM) which represents less than 4% of the overall capacity. The experimental setup, which is composed of an MCSI, a DC current source, different type of loads, a power meter, acquisition and FPGA boards, is shown in Fig. 10. The parameters of the system are the same used in the previous section.

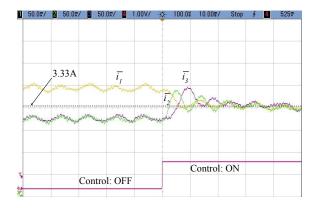

The internal filtered currents of each module  $\bar{i}_{1,2,3}$  are shown in Fig. 11 prior and post controller activation. The ripple is mainly caused by the current source that supplies the MCSI which has a ripple of approximately 2% and the zero state selection of the modulator. When the controller is disabled, the internal currents have a difference of 80mA. After the controller is enabled, the internal currents of each module show the desired response converging to 3.33A in less than 50ms

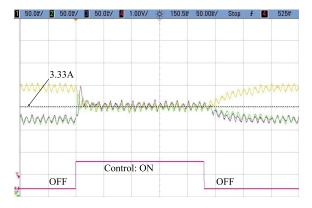

In Fig. 12, the controller is enabled and disabled again after 230ms. After being enabled, the currents of each module converge to the same value and when the control is disabled the currents return to their original value with a longer settling time. The longer settling time is caused by the open loop response of the system which depends only on the topology and the system parameters.

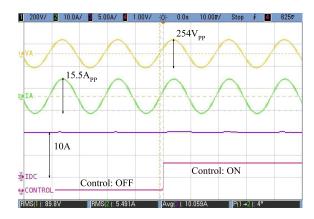

Fig. 13 shows the voltage  $v_a$ , current  $i_a$  and input current

Fig. 11. Internal average currents with and without control. Upper traces: internal average currents  $\bar{i}_{1,2,3}$  at a scale of 50mA/div. Bottom trace: control enable signal

Fig. 12. Step on control activation. Internal average currents with and without control. Upper traces: internal average currents  $\bar{i}_{1,2,3}$  at a scale of 50mA/div. Bottom trace: control enable signal

Fig. 13. Traces from top to bottom. First: output voltage  $v_a$  [V] at a scale of 200V/div. Second: output current  $i_a$  [A] at a scale of 10A/div. Third: input current  $I_{dc}$  [A] at a scale of 5A/div. Fourth: control enable signal

$i_{dc}$  along with the control enable signal. Both,  $v_a$  and  $i_a$  present a low distortion due to the multilevel capabilities of the inverter along with its high equivalent commutation frequency. There are no noticeable differences on the waveforms after the control is enabled.

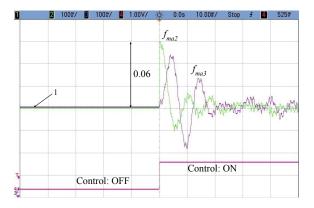

The variation of the scale factors,  $f_{ma2,3}$ , after the controller is enabled are shown in Fig. 14. They introduce a slight change in the triangular carriers to perform the balancing of

Fig. 14. Controller output signals with and without control. Upper traces:  $f_{ma2}$  and  $f_{ma3}$  at a scale of 0.02/div. Bottom trace: control enable signal

Fig. 15. THD measurement of output voltage  $v_a$  with control enabled

the internal currents. A good correlation between simulation and experimental results is observed.

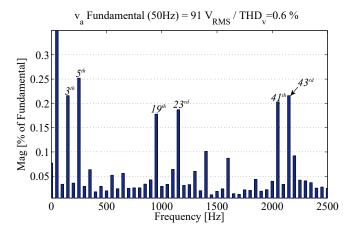

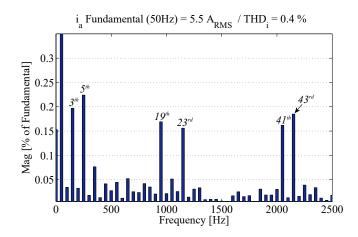

The spectrum of the output waveforms,  $v_a$  and  $i_a$  are depicted in Fig. 15 and Fig. 16 respectively. The first 50 harmonics were measured using a Fluke 435 Series II Power Quality and Energy Analyzer, according to the IEC 61000-4-7 standard. The main differences with the simulation are the presence of the third harmonic and an increment of 0.1 % in most of the harmonics. The third harmonic is introduced mainly by the ripple of the DC current source. The power differences are due to delays introduced by the semiconductor switches, accuracy and resolution of the power meter, and small errors introduced by the FPGA implementation. The THD of the current is 0.3% when the controller is disabled and increases to 0.4% when enabled. The same behavior is observed for the voltage THD that gets increased to 0.6% when the controller is enabled. Results are very promising since, even when the controller is activated, THD values are below the 3% established by the IEC 61000-4-7 and the IEEE Standard 519.

## V. CONCLUSIONS

A control technique to ensure the balance of the internal currents on an MCSI is presented. Although the implementation needs the measurement of the internal currents, it requires

Fig. 16. THD measurement of output current  $i_a$  with control enabled

little computational effort, and hence a small area on an FPGA. It also introduces a minimal distortion to the SPWM signals without affecting the switching losses and increasing less than 0.1% the THD at the output of the inverter. The controller has been designed, evaluated through simulations and implemented on a prototype of a 7 level MCSI. Simulation and experimental results show an excellent behavior. This solution can be easily expanded adding only a PI controller for each additional module.

The proposed controller is suitable for industrial converters as it can withstand disturbances and imbalances of the components without affecting the internal currents of the MCSI.

# REFERENCES

- [1] J. I. Y. Ota, T. Sato, and H. Akagi, "Enhancement of Performance, Availability, and Flexibility of a Battery Energy Storage System Based on a Modular Multilevel Cascaded Converter (MMCC-SSBC)," *IEEE Transactions on Power Electronics*, vol. 31, DOI 10.1109/TPEL.2015.2450757, no. 4, pp. 2791–2799, Apr. 2016.

- [2] D. F. Cortez and I. Barbi, "A three-phase multilevel hybrid switched-capacitor pwm pfc rectifier for high-voltage-gain applications," *IEEE Transactions on Power Electronics*, vol. 31, DOI 10.1109/TPEL.2015.2467210, no. 5, pp. 3495–3505, May. 2016.

- [3] R. Mo and H. Li, "Hybrid energy storage system with active filter function for shipboard mvdc system applications based on isolated modular multilevel dc/dc converter," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, DOI 10.1109/JESTPE.2016.2642831, no. 1, pp. 79–87, Mar. 2017.

- [4] G. Brando, A. Dannier, A. D. Pizzo, R. Rizzo, and I. Spina, "Torque derivative control in induction motor drives supplied by multilevel inverters," *IET Power Electronics*, vol. 9, DOI 10.1049/iet-pel.2014.0958, no. 11, pp. 2249–2261, 2016.

- [5] D. Zhou, J. Zhao, and Y. Li, "Model-predictive control scheme of fiveleg ac-dc-ac converter-fed induction motor drive," *IEEE Transactions on Industrial Electronics*, vol. 63, DOI 10.1109/TIE.2016.2541618, no. 7, pp. 4517–4526, Jul. 2016.

- [6] S. Du, B. Wu, N. R. Zargari, and Z. Cheng, "A flying-capacitor modular multilevel converter for medium-voltage motor drive," *IEEE Transactions on Power Electronics*, vol. 32, DOI 10.1109/TPEL.2016.2565510, no. 3, pp. 2081–2089, Mar. 2017.

- [7] N. Thitichaiworakorn, M. Hagiwara, and H. Akagi, "A medium-voltage large wind turbine generation system using an ac/ac modular multilevel cascade converter," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, DOI 10.1109/JESTPE.2015.2462119, no. 2, pp. 534–546, Jun. 2016.

- [8] C. D. Fuentes, C. A. Rojas, H. Renaudineau, S. Kouro, M. A. Perez, and T. Meynard, "Experimental validation of a single dc bus cascaded h-bridge multilevel inverter for multistring photovoltaic systems," *IEEE Transactions on Industrial Electronics*, vol. 64, DOI 10.1109/TIE.2016.2619661, no. 2, pp. 930–934, Feb. 2017.

- [9] P. Cossutta, M. P. Aguirre, A. Cao, S. Raffo, and M. I. Valla, "Single-stage fuel cell to grid interface with multilevel current-source inverters," *IEEE Transactions on Industrial Electronics*, vol. 62, DOI 10.1109/TIE.2015.2434800, no. 8, pp. 5256–5264, Aug. 2015.

- [10] M. Quraan, P. Tricoli, S. D'Arco, and L. Piegari, "Efficiency assessment of modular multilevel converters for battery electric vehicles," *IEEE Transactions on Power Electronics*, vol. 32, DOI 10.1109/TPEL.2016.2557579, no. 3, pp. 2041–2051, Mar. 2017.

- [11] D. Drews, R. Cuzner, and G. Venkataramanan, "Operation of Current Source Inverters in Discontinuous Conduction Mode," *IEEE Transactions on Industry Applications*, vol. 52, DOI 10.1109/TIA.2016.2590466, no. 6, pp. 4865–4877, Nov. 2016.

- [12] K. G. Sambandam, A. K. Rathore, A. Edpuganti, and D. Srinivasan, "Current-fed Multilevel Converters: An Overview of Circuit Topologies and Modulation Techniques," in *IEEE Industry Applications Society Annual Meeting*, DOI 10.1109/IAS.2016.7731887, pp. 1–10, Oct. 2016.

- [13] Q. Wang, M. Cheng, and Y. Jiang, "Harmonics Suppression for Critical Loads Using Electric Springs With Current-Source Inverters," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, DOI 10.1109/JESTPE.2016.2591942, no. 4, pp. 1362–1369, Dec. 2016.

- [14] R. Ramachandran and M. Nymand, "Experimental Demonstration of a 98.8% Efficient Isolated DC-DC GaN Converter," *IEEE Transactions on Industrial Electronics*, vol. PP, DOI 10.1109/TIE.2016.2613930, no. 99, pp. 1–1, 2016.

- [15] K. Armstrong, S. Das, and J. Cresko, "Wide Bandgap Semiconductor Opportunities in Power Electronics," in 4th Annual IEEE Workshop on Wide Bandgap Power Devices and Applications (WIPDA), vol. 3, DOI 10.1109/MPEL.2016.2557258, no. 2, pp. 73–73, Jun. 2016.

- [16] D. Johannesson, M. Nawaz, K. Jacobs, S. Norrga, and H.-P. Nee, "Potential of Ultra-High Voltage Silicon Carbide Semiconductor Devices," in 4th Annual IEEE Workshop on Wide Bandgap Power Devices and Applications (WIPDA), vol. 3, DOI 10.1109/MPEL.2016.2557258, no. 2, pp. 73–73, Jun. 2016.

- [17] M. Aguirre, L. Calviño, and M. Valla, "Multilevel current-source inverter with fpga control," *IEEE Trans. Ind. Electron.*, vol. 60, DOI 10.1109/TIE.2012.2185014, no. 1, pp. 3–10, Jan. 2013.

[18] M. Huang, J. Zou, and X. Ma, "An Improved Phase-Shifted Carrier

- [18] M. Huang, J. Zou, and X. Ma, "An Improved Phase-Shifted Carrier Modulation for Modular Multilevel Converter to Suppress the Influence of Fluctuation of Capacitor Voltage," *IEEE Transactions on Power Electronics*, vol. 31, DOI 10.1109/TPEL.2016.2514409, no. 10, pp. 7404–7416, Oct. 2016.

- [19] J. Ebrahimi and H. Karshenas, "A New Reduced-Component Hybrid Flying Capacitor Multicell Converter," *IEEE Transactions on Industrial Electronics*, vol. PP, DOI 10.1109/TIE.2016.2618876, no. 99, pp. 1–1, 2016.

- [20] Y. Okazaki, H. Matsui, M. Muhoro, M. Hagiwara, and H. Akagi, "Enhancement on capacitor-voltage-balancing capability of a modular multilevel cascade inverter for medium-voltage synchronous-motor drives," in *Energy Conversion Congress and Exposition (ECCE)*, 2015. IEEE, DOI 10.1109/ECCE.2015.7310550, pp. 6352–6359, Sep. 2015.

- [21] P. Raj, A. Maswood, G. Ooi, and Z. Lim, "Voltage balancing technique in a space vector modulated 5-level multiple-pole multilevel diode clamped inverter," *Power Electronics, IET*, vol. 8, DOI 10.1049/ietpel.2014.0747, no. 7, pp. 1263–1272, 2015.

- [22] Y. Okazaki, H. Matsui, M. M. Muhoro, M. Hagiwara, and H. Akagi, "Capacitor-voltage balancing for a modular multilevel dscc inverter driving a medium-voltage synchronous motor," *IEEE Transactions on Industry Applications*, vol. 52, DOI 10.1109/TIA.2016.2558638, no. 5, pp. 4074–4083, Sep. 2016.

- [23] Y. Li, E. A. Jones, and F. Wang, "The Impact of Voltage-Balancing Control on Switching Frequency of the Modular Multilevel Converter," *IEEE Transactions on Power Electronics*, vol. 31, DOI 10.1109/TPEL.2015.2448713, no. 4, pp. 2829–2839, Apr. 2016.

- [24] A. R. S, S. Pramanick, M. Boby, K. Gopakumar, and L. G. Franquelo, "Extended Linear Modulation Operation of a Common-Mode-Voltage-Eliminated Cascaded Multilevel Inverter With a Single DC Supply," *IEEE Transactions on Industrial Electronics*, vol. 63, DOI 10.1109/TIE.2016.2586441, no. 12, pp. 7372–7380, Dec. 2016.

- [25] N. Binesh and B. Wu, "5-level parallel current source inverter for high power application with dc current balance control," in *Electric Machines Drives Conference (IEMDC)*, 2011 IEEE International, DOI 10.1109/IEMDC.2011.5994649, pp. 504–509, May. 2011.

- [26] J. Bao, W. Bao, Z. Zhang, and W. Fang, "A simple current-balancing method for a three-phase 5-level current-source inverter," in *Industrial Electronics*, 2009. IECON '09. 35th Annual Conference of IEEE, DOI 10.1109/IECON.2009.5414790, pp. 104–108, Nov. 2009.

- [27] N. F. N. Ismail, N. A. Rahim, S. R. S. Raihan, and Y. Al-Turki, "Parallel inductor multilevel current source inverter with energy-recovery scheme for inductor currents balancing," *IET Power Electronics*, vol. 9, DOI 10.1049/iet-pel.2015.0909, no. 11, pp. 2298–2304, 2016.

- [28] M. Aguirre, M. Engelhardt, J. Bracco, and M. Valla, "Current balance control in a multilevel current source inverter," in *Industrial Technology (ICIT)*, 2013 IEEE International Conference on, DOI 10.1109/ICIT.2013.6505906, pp. 1567–1572, Feb. 2013.

- [29] A. Martins, V. Morais, M. Ferreira, and A. Carvalho, "Control Architecture based on FPGA for a Renewable Energy System," in *IECON 2016 42nd Annual Conference of the IEEE Industrial Electronics Society*, DOI 10.1109/IECON.2016.7793902, pp. 4048–4053, Oct. 2016.

- [30] A. Cardenas, K. Agbossou, and N. Henao, "Development of power interface with fpga-based adaptive control for pem-fc system," *IEEE Transactions on Energy Conversion*, vol. 30, DOI 10.1109/TEC.2014.2349653, no. 1, pp. 296–306, Mar. 2015.

- [31] M. Merai, M. W. Naouar, I. Slama-Belkhodja, and E. Monmasson, "Fpga-based fault-tolerant space vector-hysteresis current control for three-phase grid-connected converter," *IEEE Transactions on Industrial Electronics*, vol. 63, DOI 10.1109/TIE.2016.2581758, no. 11, pp. 7008–7017, Nov. 2016.

- [32] G. A. Matig-a, M. R. Yuce, and J. M. Redouté, "An Integrated LVDS Transmitter-Receiver System With Increased Self-Immunity to EMI in 0.18- μm CMOS," *IEEE Transactions on Electromagnetic Compatibility*, vol. 58, DOI 10.1109/TEMC.2015.2505005, no. 1, pp. 231–240, Feb. 2016.

Pablo Cossutta (M'12) received the Electronics Engineer degree from the Instituto Tecnológico de Buenos Aires (ITBA), Argentina, in 2001, with honors. He also received the Specialist on Medical Equipment Degree from ITBA in 2004. He is currently working towards his PhD in Power Electronics at ITBA.

He is engaged in teaching and research on power and industrial electronics as Associate Professor at ITBA.

**Miguel Aguirre** (M'10-SM'16) received the Electronics Engineer degree from the Instituto Tecnológico de Buenos Aires (ITBA), Argentina, in 1995, and his PhD Degree from Universidad Nacional de La Plata in 2013.

He is currently the head of the Electrical and Electronics Engineer Department at ITBA, and also engaged in teaching and research on power electronics, power quality and renewable energies as Full Professor.

**Mathias Angelico Engelhardt** (M'12) graduated with honors as an Electronic Engineer from the Instituto Tecnológico de Buenos Aires (ITBA), Buenos Aires, Argentina in 2014.

He is currently working as a Project Engineer in the Research and Development Center on Industrial Electronics (CIDEI), where he does research with Power and Industrial Electronics, and its interfaces. Mathias is also Assistant Professor at ITBA.

Mará Inés Valla (S'79-M'80-SM'97-F'10) received the Electronics Engineer and Doctor in Engineering degrees from the National University of La Plata (UNLP), La Plata, Argentina, in 1980 and 1994, respectively.

She is currently a Full Professor with the Department of Electrical Engineering, Engineering Faculty, UNLP. She is also with the Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET), Buenos Aires, Argentina. She is engaged in teaching and research on Power

Converters, Power Quality and Renewable Energies.

Dr. Valla is Co-Editor in chief of the IEEE Transactions on Industrial Electronics and member of the IEEE James H. Mulligan, Jr. Education Medal Committee. She is also a member of the Buenos Aires Academy of Engineering in Argentina.