# Digital Control for a Multiple-Stage Pulsed Current Source

Nicolás Wassinger, Student Member, IEEE, Rogelio Garcia Retegui, Member, IEEE, Marcos Funes, Member, IEEE, and Mario Benedetti

Abstract—Multiple-stage converters are composed of a set of structures with different voltage, current and switching frequency capabilities. In particular, in applications like particle accelerator beam deflection and focusing, the requirement is high-current high-precision current pulses generation. In order to satisfy the specifications of this application, a novel multiple-stage converter topology was proposed and presented in a previous work. However, said proposal should be complemented with a control system to perform the control of each structure, manage its global interconnection and execute the regulation loops. This work describes the implementation of the digital control developed for the proposed converter. Experimental results are presented by applying the proposed control to a prototype.

Index Terms—Digital control, power electronics, pulsed power converter.

### I. INTRODUCTION

ARTICLE accelerators applied to high-energy physics and clinical treatment use high-current pulsed converters to supply an inductive load made up of different types of magnets to produce a high-magnetic field that has to be constant throughout the beam length [1]–[3]. For these applications, the key aspects of these converters are current stability and precision during flat top. Current rise and fall times are not critical; yet they should be reduced so as to decrease the output Root Mean Square (RMS) current value and minimize the loss in the magnet load and its associated cooling.

Even though, for many years, the solution offered for these pulsed converters has been the use of a capacitor discharge topology [4]–[7], certain drawbacks in this system (low flexibility and high RMS load current value) created the need of a new development based on switching converters. Moreover, a trapezoidal waveform is the best solution when it comes to

Manuscript received November 30, 2011; revised March 14, 2012, May 10, 2012, and May 29, 2012; accepted September 17, 2012. Date of publication October 02, 2012; date of current version January 09, 2013. This work was supported in part by Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET), Argentina, by the Ministerio de Ciencia, Tecnología e Innovación Productiva (MINCYT), Argentina, by the Agencia Nacional de Promoción Científica y Tecnológica, Argentina, by the European Organization for Nuclear Research (CERN), Switzerland, and by the European Particle Physics Latin American Network (EPLANET). Paper no. TII-11-923.

The authors are with the Laboratorio de Instrumentación y Control (LIC), Universidad Nacional de Mar del Plata (UNMDP), 7600 Mar del Plata, Argentina, and also with CONICET, 1033 Buenos Aires, Argentina (e-mail: nwassinger@fi.mdp.edu.ar; rgarcia@fi.mdp.edu.ar; mfunes@fi.mdp.edu.ar; mbenedet@fi.mdp.edu.ar).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TII.2012.2221723

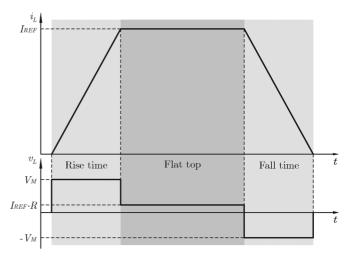

Fig. 1. Trapezoidal load current waveform and corresponding applied voltage.

reducing the RMS current in the load. This current waveform involves the application of a high voltage (with reverse polarity) during rise and fall times, which allows to reduce the duration of these stages (Fig. 1). Besides, during flat top a high-precision high-dynamic current control is required which implies switching the power semiconductors at high-frequency. These requirements (high-voltage, high-current, and high-frequency) cannot be fulfilled by conventional converters and current semiconductor devices [8]–[11].

In order to overcome this technological limitation, a novel converter topology for high-current and high-precision current sources was proposed by [12] and later improved by [13]. The power converter, denoted as a multiple-stage converter, is based on the use of different structures, each one specific for a particular operation range in terms of voltage, current, and switching frequency. These structures are connected during one or more stages of the generated waveform to accomplish the specific requirements corresponding to each stage. The control system associated to this converter must meet hard requirements. It must perform the individual control of each structure, manage the global interconnection of the several structures, and execute the regulation loops assuring minimum duration and amplitude transient response in the load current and high-precision in the flat top. Additionally, it must calculate the initialization parameters before each pulse, manage the peripheral communication and carry out communication with a more hierarchical supervision and command system, among other tasks.

Although there are many powerful digital platforms able to perform the control of multiple-stage converters, the concurrent stages management, peripheral attention and high-speed

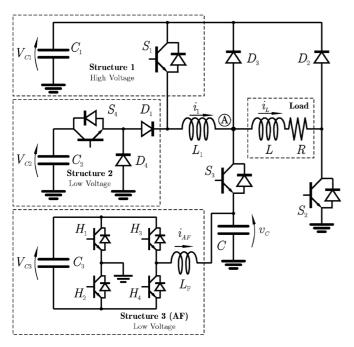

Fig. 2. Simplified scheme of the proposed topology.

calculations require the utilization of a Field Programmable Gate Array (FPGA). The use of this technology to develop and improve digital control systems is known [14]–[16] and has been well exemplified in papers like [17]–[20]. In this paper, an FPGA-based digital control for the multiple-stage converter proposed in [13] is presented. The next sections introduce the multiple-stage converter basics and highlight the most relevant aspects of the proposed control that enable to achieve the stringent requirements of the above mentioned applications. The experimental results obtained with a prototype that emulates the full scale features validate the control system implementation.

# II. POWER SOURCE DESCRIPTION

This section describes the operating principle of the topology presented in [13] to better understand the different tasks to be performed by the control system. Fig. 2 provides the general scheme of the converter which is based on three structures. The aim is to use structure 1 (High-Voltage and High-Current) during rise and fall times, structure 2 (Low-Voltage and High-Current) to control the flat top mean current with moderate precision, and structure 3 (Low-Voltage and Current) to control the load current with the required precision.

The operational principle of this topology is summarized as follows.

Rise time: During this stage, only structure 1 is activated, which initiates the charge of  $L_1$  and L through the high-voltage source  $V_{C1}$ . This condition is obtained by means of  $S_1$  and  $S_2$  turned on and  $S_3$  and  $S_4$  turned off. Besides, the use of  $D_1$  is needed to provide structure 2 high-voltage isolation. If the load resistance is considered negligible, the required voltage  $V_{C1}$  to reach the flat top current  $I_{\rm REF}$  in a rise time  $T_R$  is given by (1).

$$V_{C1} = I_{REF} \frac{L + L_1}{T_R}.$$

(1)

— Flat top: When currents  $i_L = i_1$  reach the reference value  $I_{\rm REF}$ , structure 1 is disconnected and structures 2 and 3 are connected by means of  $S_1$  turning off and  $S_3$  turning on.

Structure 2 is a one quadrant inverter composed by  $C_2$ ,  $S_4$ ,  $D_4$ , and  $D_1$  which is used to control the  $i_1$  so as to provide the mean load current. This system is modeled as a current generator called GI1 which operates in PWM mode with a commutation frequency  $f_{I1}$ . It is common knowledge that an increase of this frequency causes a decrease of the ripple current. However, due to the technological limitations of semiconductor devices,  $f_{I1}$  switching frequency is limited by the current and the voltage maximum ratings. Therefore, since structure 2 must handle the high load current, a medium  $S_4$  switching frequency must be adopted. As a consequence, a peak to peak ripple current  $\Delta I_1$ , much higher than the required one, is obtained.

Structure 3 is a full bridge inverter (composed by  $C_3$ ,  $H_1$ ,  $H_2$ ,  $H_3$ , and  $H_4$ ) connected in series with the inductance  $L_F$ . This structure, named Active Filter (AF), must operate at a switching frequency  $f_{IF}$  higher than  $f_{I1}$  in order to cancel  $\Delta I_1$ . A current ripple  $\Delta I_F$  is generated.

In order to ensure the operation of the current controls, the voltages  $V_{C2}$  and  $V_{C3}$  must be higher than  $I_{REF} \cdot R$ .

The turning on of  $S_3$  allows the connection of the active filter and the capacitor C to the node A. C is connected in parallel to structure 3 to avoid overvoltage in this node.

— Fall time: To decrease the load current, all switches are turned off. The energy stored in the load and inductor  $L_1$  returns to the capacitor bank  $C_1$  through  $D_1$ ,  $D_2$ , and  $D_4$ . The current difference between  $i_{L1}$  and  $i_L$  when  $S_3$  is turned off flows through  $D_3$  or the antiparallel diode of  $S_3$  depending on the current flow direction.

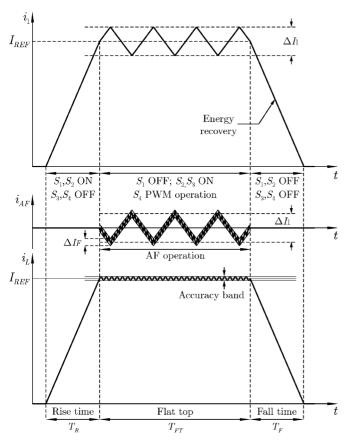

Fig. 3 illustrates the current waveforms of the proposed system and the state of the different semiconductor switches.

# III. CONTROL SYSTEM IMPLEMENTATION

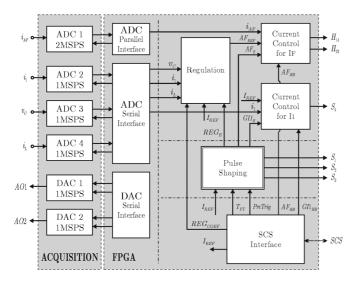

This section deals with the digital implementation of the several tasks that the control system must perform. The proposed control system is organized in hierarchical layers. The top layer performs the communication with the external supervision and command system (SCS). The following layer is in charge of pulse shaping according to the parameters provided by the SCS; and the bottom layer is composed of the current controls and the regulation loops. This latter contains the most complex and most computational intensive tasks. Additionally, the communication with the analog to digital and digital to analog converters is realized concurrently with the tasks performed in all these layers. Fig. 4 depicts a block diagram of the implemented control system. A more detailed description of these blocks, listed hierarchically, is provided next.

1) Supervision and Command System Interface: This block performs the communication with the hierarchical supervision and command system. This system receives the pulse width, the reference current, and the synchronization command (the pulse must be synchronous with other converters). This block provides the converter status as well.

Fig. 3. Current waveforms and operation principle.

Fig. 4. Block diagram of the digital control board.

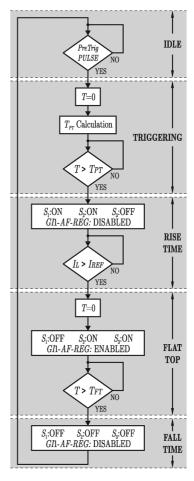

2) Pulse Shaping: This block manages the interconnection of different structures through the control of  $S_1$ ,  $S_2$ , and  $S_3$  states, and the enabling of the Current Control and Regulation Blocks. The performed tasks in the different stages are implemented by means of a state machine depicted by the flow chart in Fig. 5.

In this flow chart, it can be noticed that the system remains in idle state and goes to the triggering stage when the pretrigger command is received from the SCS block.

Fig. 5. Flow chart of the pulse control block

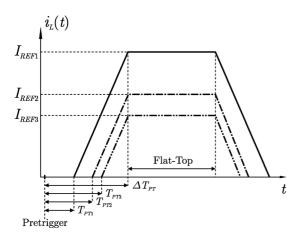

The triggering stage determines the rise time beginning. This event must be adjusted to obtain a constant delay,  $\Delta T_{\rm PT}$ , between the pretrigger signal and the flat top beginning.  $\Delta T_{\rm PT}$  is composed of two times, the delay  $T_{\rm PT}$  between the pretrigger signal and the start pulse, and the rise time  $T_R$ . Since,  $T_R$  depends on the reference current,  $T_{\rm PT}$  must be adjusted for each pulse. Fig. 6 illustrates the synchronism to different flat top currents. The pretrigger time  $T_{\rm PT}$  is calculated by means of (2)

$$T_{\rm PT} \approx \Delta T_{\rm PT} - \frac{(L+L1)I_{\rm REF}}{V_{C1}}.$$

(2)

During rise time, switches  $S_1$ ,  $S_2$ , and  $S_3$  are commanded as it was previously indicated in Section II, while current controls and regulation loops remain disable. The transition from the rise time stage to the flat top stage is performed when the condition  $i_L > i_{\rm REF}$  is satisfied. Once in the flat top, the state of the switches  $S_1$ ,  $S_2$ , and  $S_3$  change and, the current controls and the regulation loops are enabled. The transition from the flat top stage to the fall time stage is done when a timer, that starts at flat top beginning, reaches a time  $T_{\rm FT}$ . In fall time stage, all switches are turned off and, the current controls and the regulation loops are disabled.

3) Current Control Blocks: The current controls of GI1 and AF are performed by digital hysteresis controls. These controls involve the acquisition of the currents and its comparison

Fig. 6. Scheme of the discharge pulse triggering system operation.

Fig. 7. Flat top equivalent circuit.

with hysteresis bands. The presence of delays in the acquisitions leads to errors in the detection of the crosses with the bands. The magnitude of these errors depends on the current slopes. Therefore, due to the high slopes of  $i_1$  and  $i_{\rm AF}$ , high acquisition frequencies are needed.

The current controls are implemented with state machines, comparators, and counters. The switching output signal to generate the  $i_{\rm AF}$   $i_1$  current is limited in frequency to avoid switch damage.

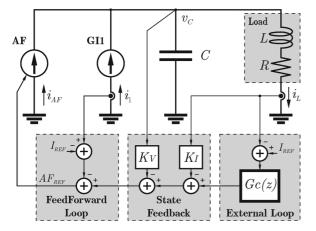

4) Regulation: As the system is made up of different interconnected structures, a transient is generated each time a structure is connected/disconnected. This aspect is critical at the beginning of the flat top, as the generated transient can exceed the system specifications of duration and amplitude. Fig. 7 illustrates an equivalent circuit of the system in the flat top. The capacitor and the load form a second order circuit with a low damping factor. If the initial conditions of the circuit are not appropriate ( $i_1 = i_L \neq I_{\rm REF}$  or  $v_C \neq I_{\rm REF} \cdot R$ ), a damped oscillatory response is generated.

In practice, the appropriate conditions are very difficult to obtain due to possible delays in the devices operation. To improve the transient response of the system, a state feedback control is proposed to place the closed loop poles of the second order circuit. This control is implemented by means of the gains of  $K_V$

Fig. 8. Feedback loops.

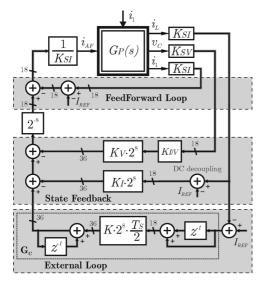

and  $K_I$ , which are estimated by means of the Ackerman method [21]. As the resulting transfer is a type-0 system, there will be a steady-state error in the mean value of  $i_L$ , which is compensated by an external loop with an integral type controller. With a view to improving  $i_1$  current ripple rejection in the flat top and to reduce the external loop requirements, a feedforward loop is incorporated by adding the difference between the  $I_{\rm REF}$  and  $i_1$ . The feedforward, state feedback, and external loops are implemented by means of the AF.

The duration and the amplitude of the load current transient error can be adjusted by setting the state feedbacks and the external loop gains. In order to obtain a transient response mainly dependent on the external loop bandwidth,  $K_I$  and  $K_V$  are adjusted to place the poles above the bandwidth. To improve the transient response, the loop gains must be adjusted, with the consequent higher control effort. This implies that the feasibility of improving the transient response is limited by the capabilities of the AF.

The control system is implemented in a Spartan-3 FPGA that provides embedded multipliers. These ones accept two 18-bit words as inputs and produce a 36-bit product. Consequently, the regulation loops are implemented using an 18-bit fixed point arithmetic format for the multipliers input variables and a 36-bit word length for the addition calculations.

In order to select the normalization constant, the signals of greatest magnitude, in this case those corresponding to blocks  $G_C$  and  $K_I$ , are determined (Fig. 8).

The block  $G_C$  output  $(i_C)$  can be divided into two components

$$i_C = \overline{I_C} + \widetilde{I_C} \tag{3}$$

where  $\overline{I_C}$  is the constant term that equals the addition of the feedbacks from  $K_V$  and  $K_I$ , and  $\widetilde{I_C}$  is the variable term that corrects  $i_L$  variations.

The constant term can be expressed as

$$\overline{I_C} = K_V \overline{V_C} + K_I \overline{I_L} = (K_V R + K_I) \cdot I_{REF} \tag{4}$$

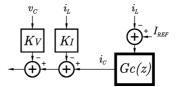

Since this term is constant and known and its magnitude is highly elevated, it is eliminated from the controller and later added as a summing stage in its output. As a result, the controller output operates at low levels of magnitude. Besides, if  $K_V R \ll K_I$ , the term  $K_V R$  can be simplified, giving rise to the schematic shown in Fig. 9.

Still there are problems associated to a resolution loss for normalization due to the fact that the  $K_I i_L$  and  $K_I I_{\rm REF}$  terms are much higher than the controller output or  $K_V v_C$ . This can be overcome by modifying the order of operations, as shown in Fig. 10. It can be observed that as  $i_L$  is close to  $I_{\rm REF}$ ,  $K_V v_C$ ,

Fig. 9. Feedback loop modification.

Fig. 10. Resultant feedback loop.

Fig. 11. Detailed implementation

$K_I i_L$  and  $G_C(z) \cdot (i_L - I_{REF})$  terms are of the same order of magnitude.

Finally feedback loops gains were normalized with a  $2^8$  factor, that is considered before the feedforward loop. Fig. 11 depicts a detailed scheme of the loops implemented in this block.

The gain blocks  $K_{SI}$  and  $K_{SV}$  include the magnitudes from the sense and the ADC conversion stages. These gains are  $K_{SI}=2^{17}/I_{\rm MAX}$  and  $K_{SV}=2^{17}/V_{\rm MAX}$ , where  $I_{\rm MAX}$  and  $V_{\rm MAX}$  represent the input dynamic ranges of the sensing system. The sensing stage gains are scaled in order to maintain the dynamic range of the digital control platform fixed regardless of the generated current value. The ADC outputs are converted from 16 to 18 bits to match the numeric format.

The factor  $K_{I/V}$  before the  $K_V$  block adjusts a gain difference between  $K_{SV}$  and  $K_{SI}$ . The  $i_{\rm AF}$  generator is represented with the gain  $1/K_{SI}$ .

5) ADC and DAC Interface Blocks: The acquisition module consists of four ADC converters with their corresponding differential input filters. The 16-bit ADC converters are used to acquire  $i_1$ ,  $i_L$  and  $v_C$  at 1 MSPS with serial communication and

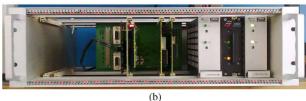

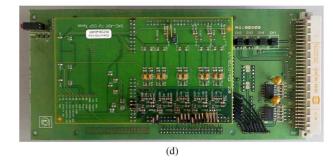

Fig. 12. Photos of the control system implementation. (a) Converter prototype (Current Scale 1:100). (b) Control system rack (control system board and power supplies). (c) Control system board–front side (Xilinx FPGA development kit). (d) Control system board–back side (acquisition and debugging board).

$i_{\rm AF}$  at 2 MSPS with a parallel one. This board is also equipped with two DAC converters able to generate test signals to debug the system. The blocks used to command the ADC and DAC converters are implemented with state machines that work at 40 and 20 MHz, respectively.

# IV. EXPERIMENTAL RESULTS

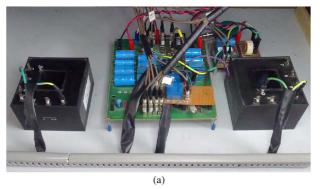

In order to validate the proposed topology and the associated control system, a low scale prototype was developed [Fig. 12(a)]. This prototype was designed based on the full scale converter specifications (Table I) proposed in [13]. The current and voltage values of the prototype were scaled down to laboratory levels (~100 times). Even though this downscaling would allow to operate the prototype with frequencies higher

TABLE I FULL SCALE PROTOTYPE PARAMETERS

| L                 | 1 mH                | $I_{REF}$              | 2000 A        |

|-------------------|---------------------|------------------------|---------------|

| R                 | $0.15~\Omega$       | $T_R, T_F$             | < 1  ms       |

| $L_1$             | $500~\mu\mathrm{H}$ | Settling time $T_{ST}$ | $< 200~\mu s$ |

| $L_F$             | $50~\mu\mathrm{H}$  | Flat top duration      | 3 ms          |

| C                 | $4\mu\mathrm{F}$    | Current precision      | 500 ppm       |

| $V_{C1}$          | 3000 V              | $f_{I1}$               | 10 KHz        |

| $V_{C2} = V_{C3}$ | 600 V               | $f_{IF}$               | 100 KHz       |

TABLE II LOW SCALE PROTOTYPE PARAMETERS

| $\overline{L}$    | 1 mH                | $I_{REF}$              | 15 A          |

|-------------------|---------------------|------------------------|---------------|

| R                 | $0.15~\Omega$       | $T_R, T_F$             | < 1 ms        |

| $L_1$             | $500~\mu\mathrm{H}$ | Settling time $T_{ST}$ | $< 200~\mu s$ |

| $L_F$             | $50~\mu\mathrm{H}$  | Flat top duration      | 3 ms          |

| C                 | $4\mu\mathrm{F}$    | Current precision      | 500 ppm       |

| $V_{C1}$          | 20 V                | $f_{I1}$               | 10 KHz        |

| $V_{C2} = V_{C3}$ | 10 V                | $f_{IF}$               | 100 KHz       |

than those indicated in Table I, the switching frequencies and the relevant times  $(T_R, T_F \text{ and } T_{ST})$  were kept as in this table. The main parameters of the low scale prototype are listed in Table II

Note that the differences between these prototypes are given by the power and the sensing stages while the developed control platform is valid for both systems. Therefore, the prototype could be used like a simulator for this platform.

The control system was developed to be mounted on a 2U rack [Fig. 12(b)]. To test it, a FPGA development Kit of Xilinx [Fig. 12(c)] together with a custom acquisition and debugging board that includes ADC and DAC converters [Fig. 12(d)] were used. An additional board was used to link and connect them to the rack. The latter also provides the circuitry necessary to adapt the levels of the switch command signals. Currently, a single board containing the complete control system is under development.

The control was described in VHDL and implemented in a Xilinx FPGA Spartan 3 (3S200FTG256-5) with ISE software [22]. This FPGA contains a total of 1920 slices and 12 18-bit dedicated multipliers. Resources utilization was around 39%, and it included 3 out of the 12 available multipliers. The design was defined with timing constrains to assure the time specifications of the acquisitions and the regulation loops. The main clock used was of 160 MHz which was generated from the external 50 MHz clock using a Digital Clock Manager.

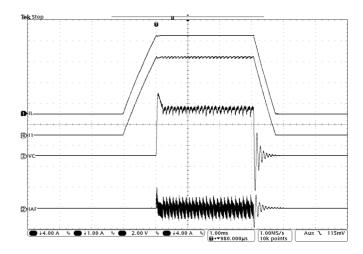

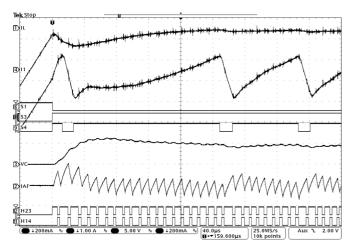

Fig. 13 displays the more relevant signals of the topology when a 15 A pulse with a 3.5 ms flat top time is generated. Load current  $i_L$ , GI1 generator current  $i_1$ , capacitor voltage  $v_C$  and active filter current  $i_{\rm AF}$  are arranged from the top downwards. As it can be observed, pulse generation presents no oscillations or significant variations during the coupling of structures (beginning and end of the flat top), as expected. In addition, times  $T_R=1$  ms and  $T_F=0.6$  ms were within specifications. It can be seen that  $T_R$  was greater than  $T_F$  because, during the rise time, the forward voltage of the devices and  $V_{C1}$  have an

Fig. 13. Waveforms of the more relevant voltage and current signals.

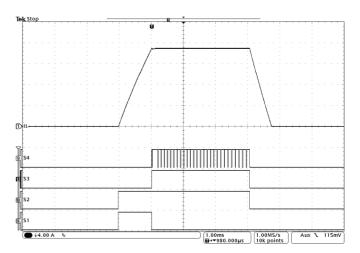

Fig. 14. Waveforms of the  $i_L$  current and  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$  control signals.

opposite polarity, while during the fall time they have the same polarity.

Fig. 14 depicts the load current together with the signals to drive the  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$  switches. The states of the switches associated to each pulse generation stage can be seen; and the difference between the commutation frequencies of the switches noticed.

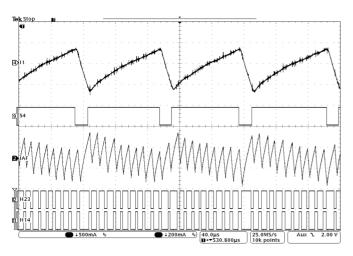

A detail view of the signals at the beginning of the flat top is illustrated in Fig. 15.  $i_L$  and  $i_1$  currents, command signals for  $S_1$ ,  $S_3$  and  $S_4$ , voltage  $v_C$ , current  $i_{\rm AF}$  and signals to control the active filter are arranged from the top downwards. This figure shows that a transient response in the load current is produced as previously described in Section III-A4. In this test, the worst case was evaluated, which corresponds to the connection of the capacitor initially discharged. This condition generates a transient response with a drop in the load current. By means of the compensation strategy applied, the transient response has been adjusted so as to obtain a damped response with a settling time below 200  $\mu$ s, thereby meeting the specifications. During the transient response it can also be noticed, that variations in  $v_C$  change the slopes of  $i_1$ , which temporarily modifies its switching period.

Fig. 15. Waveforms of the more relevant voltage, current and switch control signals at the flat top beginning.

Fig. 16. Current waveforms generated by GI1 and AF and its corresponding control signals once the transitory was finished.

Fig. 16 exhibits the currents of the GI1 (top) and AF (bottom) generators during the flat top once the transient response is extinguished. In addition, together with each of these, the switch command signals are displayed. Note that the commutation frequency of the GI1 and AF are closed to 10 and 100 KHz, respectively. It can be noted that, as the active filter must cancel the GI1 ripple, the average value of  $i_{\rm AF}$  results approximately equal to the inverse of the  $i_1$  ripple.

## V. CONCLUSION

This paper describes the most relevant aspects of the digital control system implementation developed for a multiple-stage converter. The proposed control, based on FPGA technology, enables the management of the several converter structures assuring the requirements of minimum duration and amplitude transient response in the load current and high-precision in the flat top. This control, associated to a previously proposed converter topology, makes the power source suitable for the generation of high-current pulses with high precision in the flat top and low rise and fall times. Tests performed with a prototype validate the proposal.

#### REFERENCES

- [1] H. Xiao, L. Li, H. Ding, T. Peng, and Y. Pan, "Study on a highly stabilized pulsed power supply for high magnetic fields," *IEEE Trans. Power Electron.*, vol. 26, no. 12, pp. 3817–3822, Dec. 2011.

- [2] E. Nakamura, M. Takayama, and S. Yabukami, "Fast beam injection and ejection method using a short-pulsed septum magnet for Hadron accelerators," *Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, Elsevier*, vol. 640, no. 1, pp. 29–37, Jun. 2011.

- [3] M. Watanabe, J. Kamiya, and T. Takayanagi, "Design and circuit simulation of a magnetic switching system for kicker magnet power supply of 3 GeV RCS in J-PARC," *IEEE Trans. Appl. Supercond.*, vol. 20, no. 3, pp. 1681–1684, Jun. 2010.

- [4] H. Ding, C. Jiang, T. Ding, Y. Xu, L. Li, X. Duan, Y. Pan, and F. Herlach, "Prototype test and manufacture of a modular 12.5 MJ capacitive pulsed power supply," *IEEE Trans. Appl. Supercond.*, vol. 20, no. 3, pp. 1676–1680, Jun. 2010.

- [5] T. Ding, H. Ding, T. Peng, X. Han, J. Xie, and L. Li, "Design of multipulse power supply for small pulsed high magnetic field device," *IEEE Trans. Appl. Supercond.*, vol. 20, no. 3, pp. 1689–1692, Jun. 2010.

- [6] L. Li, T. Peng, H. Ding, X. Han, T. Ding, L. Qiu, Y. Lv, Y. Song, X. Duan, F. Herlach, and Y. Pan, "The development of high performance pulsed magnets of the prototype facility of WHMFC," *IEEE Trans. Appl. Supercond.*, vol. 20, no. 3, pp. 676–679, Jun. 2010.

- [7] T. Ding, J. Wang, H. Ding, L. Li, B. Liu, and Y. Pan, "A 35 ka disc-shaped thyristor dc switch for batteries power supply of flat-top pulsed magnetic field," *IEEE Trans. Appl. Supercond.*, vol. 22, no. 3, p. 5400404, Jun. 2012.

- [8] A. Sanchez-Ruiz, M. Mazuela, S. Alvarez, G. Abad, and I. Baraia, "Medium voltage; high power converter topologies comparison procedure, for a 6.6 kV drive application using 4.5 kV IGBT modules," *IEEE Trans. Ind. Electron.*, vol. 59, no. 3, pp. 1462–1476, Mar. 2012.

- [9] V. Smet, F. Forest, J. Huselstein, F. Richardeau, Z. Khatir, S. Lefebvre, and M. Berkani, "Ageing and failure modes of IGBT modules in high-temperature power cycling," *IEEE Trans. Ind. Electron.*, vol. 58, no. 10, pp. 4931–4941, Oct. 2011.

- [10] F. Filsecker, R. Alvarez, and S. Bernet, "Comparison of 4.5-kv press-pack IGBTs and IGCTs for medium-voltage converters," *IEEE Trans. Ind. Electron.*, vol. 60, no. 2, pp. 440–449, Feb. 2013.

- [11] N. Luther-King, E. Narayanan, L. Coulbeck, A. Crane, and R. Dudley, "Comparison of trench gate IGBT and CIGBT devices for increasing the power density from high power modules," *IEEE Trans. Power Electron.*, vol. 25, no. 3, pp. 583–591, Mar. 2010.

- [12] E. Dallago, G. Venchi, S. Rossi, M. Pullia, T. Fowler, and U. Nielsen, "The power supply for a medical synchrotron beam chopper system," in *Proc. 34th Annu. Conf. IEEE Ind. Electron., IECON'08*, 2008, pp. 1016–1020.

- [13] N. Wassinger, S. Maestri, R. Retegui, J. Cravero, M. Benedetti, and D. Carrica, "Multiple-stage converter topology for high-precision high-current pulsed sources," *IEEE Trans. Power Electron.*, vol. 26, no. 5, pp. 1316–1321, May 2011.

- [14] E. Monmasson, L. Idkhajine, M. Cirstea, I. Bahri, A. Tisan, and M. Naouar, "FPGAs in industrial control applications," *IEEE Trans. Ind. Informat.*, vol. 7, no. 2, pp. 224–243, May 2011.

- [15] C. Buccella, C. Cecati, and H. Latafat, "Digital control of power converters—A survey," *IEEE Trans. Ind. Informat.*, vol. 8, no. 3, pp. 437–447, Aug. 2012.

- [16] H. Guzmán-Miranda, L. Sterpone, M. Violante, M. Aguirre, and M. Gutiérrez-Rizo, "Coping with the obsolescence of safety- or mission-critical embedded systems using FPGAs," *IEEE Trans. Ind. Electron.*, vol. 58, no. 3, pp. 814–821, Mar. 2011.

- [17] A. Gomperts, A. Ukil, and F. Zurfluh, "Development and implementation of parameterized FPGA-based general purpose neural networks for online applications," *IEEE Trans. Ind. Informat.*, vol. 7, no. 1, pp. 78–89. Feb. 2011.

- [18] M. P. Aguirre, L. Calvino, and M. I. Valla, "Multilevel current-source inverter with FPGA control," *IEEE Trans. Ind. Electron.*, vol. 60, no. 1, pp. 3–10, Jan. 2013.

- [19] M. Akiyama, T. Sakugawa, S. Hosseini, E. Shiraishi, T. Kiyan, and H. Akiyama, "High-performance pulsed-power generator controlled by FPGA," *IEEE Trans. Plasma Sci.*, vol. 38, no. 10, pp. 2588–2592, Oct. 2010.

- [20] Z. Shu, Y. Guo, and J. Lian, "Steady-state and dynamic study of active power filter with efficient FPGA-based control algorithm," *IEEE Trans. Ind. Electron.*, vol. 55, no. 4, pp. 1527–1536, Apr. 2008.

- [21] K. Ogata, Modern Control Engineering, 5th ed. Englewood Cliffs, NJ: Prentice-Hall, Sep. 2010.

- [22] Spartan-3 Generation FPGA User Guide, UG331 (v1.8), XILINX, Jun. 2011

Nicolás Wassinger (S'11) was born in Buenos Aires, Argentina, in 1984. He received the electronics engineer degree from the Universidad Nacional de Mar del Plata (UNMDP), Mar del Plata, Argentina, in 2008, where he is currently working towards the Doctor of Engineering degree.

He is currently a member of the Consejo Nacional de Investigaciones Científicas y Técnicas (CON-ICET), Buenos Aires. His research interests are in the field of power converters and digital signal processing.

Rogelio Garcia Retegui (M'12) was born in Tandil, Argentina, in 1977. He received the Ing. and Dr.Ing. degrees in electronic engineering from the Universidad Nacional de Mar del Plata (UNMdP), Mar del Plata, Argentina, in 2003 and 2009, respectively.

In 2003, he joined the Laboratorio de Instrumentación y Control, Departamento de Electrónica, UNMdP, as a Research Assistant. Since 2003, he has been an Assistant Professor at UNMdP. He is currently a Research Assistant with the National Scientific and Technical Research Council (CON-

ICET), Buenos Aires, Argentina. His current research interests include power electronics, current control, and digital signal processing.

Marcos Funes (M'12) was born in Mar del Plata, Argentina, in 1974. He received the B.S. degree in electronics engineering and the Ph.D. degree in electronics from the Universidad Nacional de Mar del Plata (UNMDP), Mar del Plata, Argentina, in 1999 and 2007, respectively.

In 1999, he joined the Department of Electronics, Universidad Nacional de Mar del Plata (UNMDP), as an Assistant Professor and Research Assistant. Since 2009, he has been with the Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET) as

a Research Assistant. His current research interests include high density programmable logic devices, power line communication, and digital signal processing.

Mario Benedetti was born in Italy in 1945. He received the Ing. degree in telecommunications engineering from the Universidad Nacional de La Plata, La Plata, Argentina, in 1968.

From 1968 to 1983, he was with the Laboratorio de Electrónica Industrial, Control e Instrumentación, Universidad Nacional de La Plata, working on developing electronic instruments. From 1970 to 1983, he was also an Associate Professor with the Department of Electrical Engineering at the same university. He spent two years as a Fellow at the Conseil Europeen

pour la Recherche Nucleaire, Geneva, Switzerland. Since 1985, he has been a Full Professor with the Department of Electrical Engineering, Universidad Nacional de Mar del Plata, Mar del Plata, Argentina. He is currently the Head of the Laboratorio de Instrumentación y Control, Departmento de Electrónica, Universidad Nacional de Mar del Plata, and a member of the National Scientific and Technical Research Council (CONICET), Buenos Aires, Argentina. He has served as a Lecturer for numerous short courses presented to the industry and other universities. His current research interests include power electronics and FMC