# Step down DC/DC converter for micro-power medical applications

Matías R. Miguez<sup>1</sup> · Alfredo Arnaud<sup>1</sup> · Alejandro Raúl Oliva<sup>2</sup> · Pedro Julián<sup>2</sup>

Received: 8 April 2016/Revised: 30 June 2016/Accepted: 8 August 2016/Published online: 13 August 2016 © Springer Science+Business Media New York 2016

Abstract In this work, a micropower step down DC/DC converter aimed at reducing the supply voltage in implantable medical devices is presented. The circuit was designed and fabricated in a 0.6  $\mu$ m technology. The DC/DC converter was tested for a wide range of input voltages between 1.9 and 5 V, output voltages between 200 mV and 1.5 V, and different load currents between 50 and 200  $\mu$ A. In all cases the output voltage was regulated with less than 3 % error and 5 % ripple.

**Keywords** DC/DC converter · Low power · Medical applications · Implantable medical devices

# **1** Introduction

In recent years, there has been a remarkable increase in the research and development of new implantable devices for the treatment of different pathologies where a major requirement is the efficient use of the energy stored in the battery. For rechargeable implants, low power consumption increases the time between charges, thus improving patient's comfort and the device reliability. For active implants with a primary battery, a change of battery requires a minor surgical procedure, therefore the battery must last as long as possible. Different methods have been suggested to reduce power consumption of implantable electronics; one of the simplest, and highly effective is reducing the supply voltage  $V_{DD}$  as much as possible. In the case of digital circuits it is well known that power consumption is proportional to  $V_{DD}^2$ . Analog circuits may also benefit from a low  $V_{DD}$  because the performance in terms of noise, and bandwidth, among other characteristics, is generally related to current consumption rather than to power consumption [1].

In most implantable medical devices, the power supply is either a primary battery of approximately  $V_{BAT} = 2.8 V$ nominal voltage, or a rechargeable one of approximately  $V_{BAT} = 4.2$  V nominal battery voltage.  $V_{BAT}$  may vary by a few hundreds of mV during normal operation from the beginning to the end of battery life/charge battery condition. A typical lithium iodine pacemaker battery can be used down to 2 V, and in the upper extreme, a fully charged lithium secondary cell can reach almost 5 V. But on the other hand, such high voltages are not strictly necessary to power the circuitry inside modern implants. Modern digital circuits can be powered with a  $V_{DD}$  as low as 0.9 V or even less for an off the shelf microcontroller [2], meanwhile, very low voltage processors have been reported in research works like [3, 4]. Also many high performance analog amplifiers, filters, and ADCs, with a supply voltage starting at a few hundred mV have been also reported. Because the battery voltage  $V_{BAT}$  is fixed (given by the battery's technology), V<sub>DD</sub> must be lowered by means of an efficient DC/DC converter to fully exploit the available battery energy.

To reduce the supply voltage in a medical implantable device, an efficient DC/DC converter with a typical load power consumption restricted from a few to a few hundred  $\mu$ Watts must be included. But while DC/DC converters are employed in most electronic devices, very few micro-power converters are reported. DC/DC converters can

Matías R. Miguez mrmiguez@gmail.com

<sup>&</sup>lt;sup>1</sup> Electrical Engineering Department, Universidad Católica, Montevideo, Uruguay

<sup>&</sup>lt;sup>2</sup> Departamento de Ingeniería Eléctrica y Computadoras, Universidad Nacional del Sur, Bahía Blanca, Argentina

be classified into switched capacitor (charge pumps) and switched inductor converters. Charge pumps have been traditionally employed for implantable electronics and other ultra-low-power applications [1, 5-8] for the sake of simplicity, and because efficiencies close to 90 % or more can be achieved for power consumption in the range of µWatts or less. However, charge pumps regularly require the use of a large number of external capacitors (in the case of efficient micro-power converters), and the output voltage is limited to certain fixed values. Inductive DC/DC converters instead require only two external components (an inductor and a capacitor) and a single output pad. Traditionally these kind of converters have been limited to power consumption above 1mW in the best case. While there are thousands of integrated circuits and complete modules in the market implementing switched-inductor DC/DC converters, it is only very recently that a few commercial products [9, 10] were introduced, and a few published circuits [3, 11-13] have been reported, implementing efficient micro-power DC/DC converters with switched inductors (efficiencies  $\eta \approx 60-90$  % are reported in the cited references). In [3] a micro-power inductive DC/DC converter is presented, that supplies voltage for the digital core of a medical system-on-chip with  $V_{DD}$ ranging from 0.5 to 1.0 V that achieves its best efficiency close to 90 %. However, the efficiency strongly depends on the operating point.

In this work, a micro-power inductive DC/DC stepdown converter is presented, aimed at powering a low noise analog amplifier that consumes  $I_{DD} = 100\mu$ A with a supply voltage of  $V_{DD} = 0.6$  V. The strategy presented in [1] is used to minimize the power consumption of the amplifier. However, in this case a discontinuous-conduction-mode (DCM) inductive DC/DC converter will substitute the charge pump converter, to minimize the number of circuit pads. The proposed DC/DC converter follows the topology presented in [3], but a different control strategy is used to avoid the appearance of spectral components of the switcher within the range of interest of the signal to be amplified (200–5 kHz). The circuit was fabricated in a 0.6 µm technology, and tested.

#### 2 DC/DC converter circuit design

## 2.1 Step down DC/DC converter basic topology

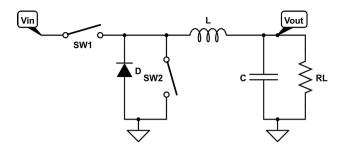

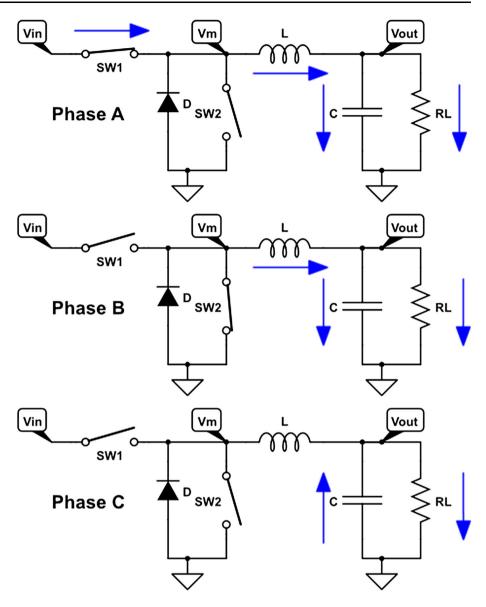

The basic topology of a step down DC/DC converter is shown in Figs. 1 and 2, the later showing the position of the switches in each phase of operation and the direction of the current flow. It should be noted that a classic step down with a large output current may consist of only two phases when operating in the continuous conduction mode (CCM); but in the case of very low output power, the DCM DC/DC

Fig. 1 Topology of a standard step down DC/DC converter

converter incorporates a third phase where the current through the coil is null for a significant fraction of the time [14]. The system works better in DCM as the total power consumption is really low, and for the selected inductance, the switching frequency would be inadequate.

The switch SW<sub>1</sub> is periodically closed at the beginning of phase A, connecting the battery to the inductor. In this phase the battery ( $V_{IN} = V_{BAT}$ ) discharges into the inductor that stores energy while it current increases; the capacitor replenishes its charge while the inductor's current is larger than the load current.

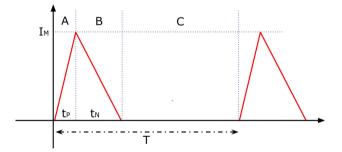

When the switch  $SW_1$  opens, phase B starts. The current continues to flow through the inductor that forward-bias the diode. In this phase the energy stored in the inductor is transferred to the capacitor and the load. A plot of the inductor current I<sub>M</sub> in an ideal case is shown in Fig. 3. To control the output voltage, the switching frequency  $f_S = 1/2$ T and the time tp that the switch is closed can be adjusted. To reduce the voltage drop in the diode, a second switch SW<sub>2</sub> is connected in parallel with D (D is actually the parasitic junction diode of SW<sub>2</sub>). SW<sub>2</sub> must be closed a short time after SW<sub>1</sub> opens and opened when the current through the inductor is zero (to prevent draining of current from the capacitor). Several DC/DC converters incorporate a specific Zero-Cross Detection (ZCD) circuit block to detect this condition. This is extremely important, as a delay in opening SW<sub>2</sub> results in a huge loss of efficiency. Energy that was already delivered to the capacitor (with losses) is now being removed, and wasted. During phase C, both switches are open and the load drains current from the capacitor.

Assuming no losses, the output voltage can be calculated by equating the input power to the output power. After some calculations:

$$V_{OUT} = \frac{R_L V_{IN} t_p^2}{4LT} \left( \sqrt{1 + \frac{8LT}{R_L t_p^2}} - 1 \right)$$

(1)

where  $R_L$  is the load (modeled as a resistor),  $t_p$  is the time the switch SW<sub>1</sub> is closed, L is the inductance and T is the switching period, as defined in Fig. 2. Equation (1) shows that the output voltage is a function of the load; therefore, an active control mechanism is required. In general this **Fig. 2** DC/DC converter in the three different phases. Current flows into the capacitor during *phases A* and *B*, and out of it in phase *C*

**Fig. 3** Current through the inductor L in a step down DC/DC converter A—SW<sub>1</sub> closed SW<sub>2</sub> open; B—SW<sub>1</sub> open SW<sub>2</sub> closed; C—SW<sub>1</sub> and SW<sub>2</sub> open

mechanism includes a low-power comparator, to compare between  $V_{OUT}$ , an external reference voltage  $V_{Ref}$ , and a feedback loop to null the error signal.

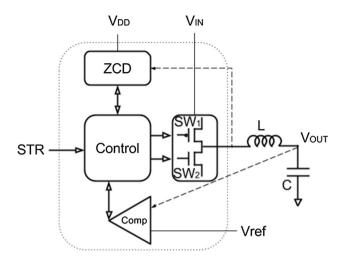

## 2.2 Designed circuit

The complete implemented circuit is shown in Fig. 4. It consists of an output stage  $SW_1$ – $SW_2$ , a comparator, a zero-crossing detector (ZCD) and the control logic. The output stage comprises two large transistors (the PMOS is  $SW_1$  and the NMOS is  $SW_2$ , having  $W = 100 \ \mu m$  and  $L = 1 \ \mu m$ ) that are turned on/off by the control circuit. This size ensures a low on resistance ( $R_{ON}(SW_1) \approx 140 \ \Omega$  and  $R_{ON}(SW_2) \approx 50 \ \Omega$ ) while allowing fast switching.

The comparator was implemented using an uncompensated miller amplifier, similar to the one presented in [15], while the inductor (L = 100  $\mu$ H) and capacitor (C = 47 nF– 200 nF) are external components. Using external components allows for lower switching frequencies, reducing the dynamic losses due to switching, and enable de use of higher quality inductors. A fully integrated (monolithic) solution would

**Fig. 4** Topology of the designed DC/DC converter. The dotted line indicates the limits between the integrated and non integrated circuit elements. The supply voltage ( $V_{DD}$ ) may be different that the input voltage ( $V_{IN}$ ) In this circuit the PMOS is  $SW_I$  and the NMOS is  $SW_2$ .STR is a adigital signal used to turn ON the DC/DC circuit

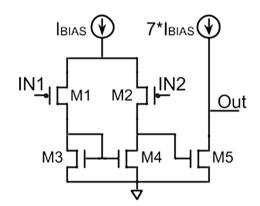

**Fig. 5** Schematic of the comparator. Power consumption was minimized in favor of comparator speed, resulting in a bigger voltage ripple

have one less pad and two less external components but was not selected for this case. A 50 nA current source (I<sub>BIAS</sub>) is required for the comparator. Figure 5 shows the schematic of the comparator. M1, M2 and M3, M4 are matched transistors sized (W/L)<sub>1,2</sub> = 10  $\mu$ m/6  $\mu$ m, and (W/L)<sub>3,4</sub> = 25  $\mu$ m/3  $\mu$ m respectively, while M5 is slightly wider with (W/ L)<sub>5</sub> = 30  $\mu$ m/3  $\mu$ m. The trade-off between power consumption and comparator speed was carefully analyzed. If the comparator is too slow, too much charge is transferred to the capacitor during charging phases, which results in a bigger voltage ripple. Since the amplifier to be powered has a large power supply rejection ratio (PSRR) and low power was the priority, a larger ripple voltage was accepted; however, the design criteria could be modified for different applications.

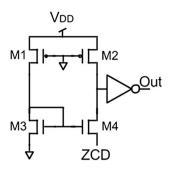

The zero-crossing detection was adapted for this application based on the one implemented in [3]. Figure 6 shows

Fig. 6 Schematic of the ZCD circuit. *M1* and *M2* gate can be used to turn off the ZCD circuit

the schematics of the ZCD block. In the schematic M3 and M4 in Fig. 6 are identical while M1 and M2 are slightly asymmetric, as an early detection is preferred. The ZCD works comparing the currents through M2 and M4. The current through M4 depends on the voltage at M4 source.

The control block is an asynchronous digital circuit that begins operation on the negative edge of the digital input STR (STR is the turn on signal). It shall firstly close the PMOS switch for a fixed time of approximately 100 ns (phase A). This time delay was generated using an asymmetric inverter chain [16]. After the PMOS switch opens, the NMOS switch closes, and it remains closed until the ZCD circuit indicates that the current through L is zero (phase B). Finally, the NMOS switch opens, and the circuit waits a fixed time of approximately 250 ns before checking the comparator. This delay was incorporated to minimize the effect of the used low-power, slow comparator. The control logic then checks if the output voltage falls below the reference, to determine if another pulse is required. As the comparator is slow, the system delivers several pulses in a short burst, and then becomes idle for a longer time while the capacitor discharges. This strategy of pulse bursts pushes the switching frequency well above the load's bandwidth. A regular distribution of the pulses, usual in this family of converters, was also simulated, and it interfered in some cases with the 200 Hz-5 kHz band of interest. On the other hand, the proposed strategy results in a higher ripple.

#### 2.3 Micro-power considerations

For this micro-power DC/DC converter, efficient circuit blocks consuming as little power as possible are required. The comparator was designed to consume less than 0.5  $\mu$ A. The ZCD circuit consumption is higher, so to reduce the total average power consumption, it is only turned on as required (during phase B). Finally, a low power logic family standard cell library, provided by the foundry, was used for the control circuitry.

Another very important aspect is to eliminate any shortcircuit current through  $SW_1$ - $SW_2$ . A short dead time

Fig. 7 Simulated start-up sequence of the DC/DC converter. Detail of one of the charging bursts

ensuring that  $SW_1$  opens before  $SW_2$  closes was introduced, to guarantee that both switches are never simultaneously closed. During the dead time, the inductor's current flows through the parasitic diode of  $SW_2$ .

## 2.4 Final considerations and simulated results

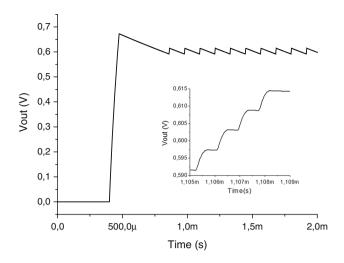

The complete circuit requires both a current reference and a voltage reference. Previous works [17] show that these circuits can be implemented with a consumption much smaller than that of the DC/DC converter. Figure 7 shows the simulated transient response of the DC/DC converter. The STR signal is switched 400  $\mu$ s after the start of the simulation and in less than 100  $\mu$ s, the circuit is working correctly. In the inset, a detail of the four charging burst is shown.

The maximum simulated current peak was less than 3 mA, which does not result in a significant variation of the rechargable battery, for example a Quallion QL0100 [18].

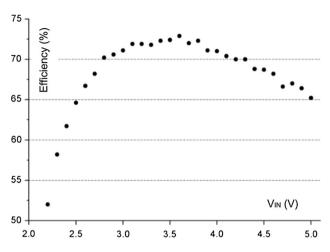

Figure 8 shows the simulated DC/DC converter eficiency for different input voltages  $V_{IN}$ , with a constant ouput voltage  $V_{OUT} = 0.6$  V and a constant load consuming 72  $\mu$ W. The efficiency achieves values over 70 % for a wide input voltage range.

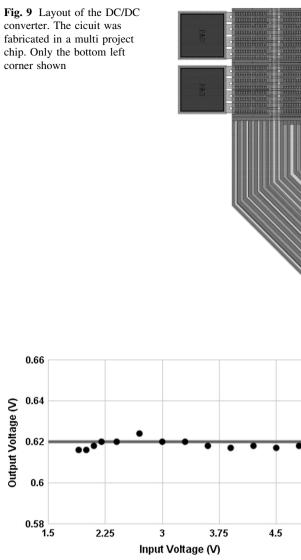

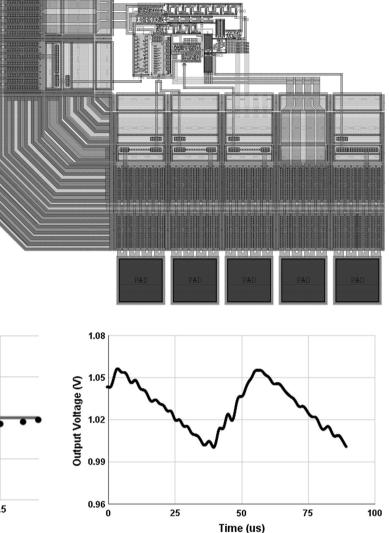

The circuit occupied a total die area of 150  $\mu$ m by 250  $\mu$ m excluding pads, and a total die area of 1000  $\mu$ m by 650  $\mu$ m including pads and all ESD protections. The circuit was located in the corner of a MPW die, as shown in Fig. 9.

## **3** Measurements

The DC/DC converter was fabricated in a 0.6  $\mu$ m process, and tested under several operating conditions. An efficient inductor with low resistance [19] and a low leakage capacitance were used in the circuit for test purposes.

Fig. 8 Simulated efficiency with a  $V_{OUT} = 0.6 \text{ V}$  and a 72  $\mu$ W consumption, for different input voltages  $V_{IN}$

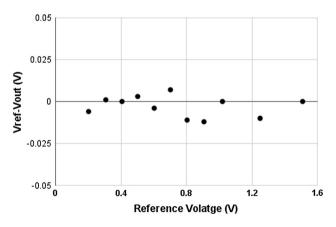

Several measurements were obtained, for  $V_{IN}$  ranging from 1.9 to 5 V, covering a wide range of possible batteries and charge conditions. The DC/DC converter was tested for different  $V_{OUT}$  conditions, ranging from 200 mV to 1.5 V. The output followed in all cases the reference voltage with less than 10 mV error. The following plots and data correspond, unless noted, to the typical test condition of  $V_{IN} = 3.3$  V, a  $V_{OUT} = 0.6$  V, and a resistive load of 6.5 k $\Omega$  at the output resulting in a nominal output power of 55  $\mu$ W. Figure 10 shows the line regulation, with a reference voltage  $V_{Ref} = 0.62$  V (gray line). The DC/DC converter exhibits a variation of less than 5 mV for an input voltage range from 1.8 to 5 V.

Figure 11 shows the difference between the reference voltage  $V_{Ref}$  and the output voltage  $V_{OUT}$ , which is always less than 10 mV while varying  $V_{Ref}$ , and keeping a fixed  $V_{IN} = 3.3$  V.

Figure 12, shows a close up of the output voltage waveform with a reference  $V_{Ref} = 1.03$  V. In the positive slope, the capacitor is being charged by a pulse burst, while the descending slope corresponds to the discharge of the output capacitor through the load. The ripple voltage is 50 mV (around 5 %) as expected, with an approximately 20 kHz frequency. This switching frequency is well above the range of the signals of interest for the amplifier (200 Hz–5 kHz), so no extra switching noise in introduced.

#### 3.1 Efficiency measurements

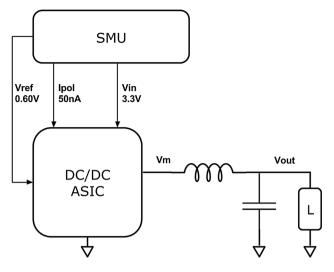

The measured efficiency was around 40 % in most cases, lower than the simulated 60–75 %. Being the only measurements that did not completely agree with the simulated results. In Fig. 13 the measurement setup used is presented. The Agilent U2722A SMU was used to generate the bias current and the input voltage  $V_{IN}$ , while a standard digital oscilloscope was used to measure both the output voltage

Fig. 10 Output voltage in terms of the input voltage, note the output is almost independent of the input

Fig. 11 Difference between the reference and output voltages, as a function of the reference voltage for a constant input voltage and load

Fig. 12 A detail of a measured output voltage transient showing 50 mV ripple @ 19 kHz

and the internal Vm voltage. The system efficiency was measured for several values of V<sub>IN</sub>, V<sub>Ref</sub> and Loads, resulting in  $\eta \approx 40$  %.

With a 3.3 V supply voltage, 0.64 V output voltage and a resistive load of 6.5 k $\Omega$ , the simulated efficiency was 70 %. In the same test condition the measured power consumption of the control loop (all the circuits except the output stage) was 21  $\mu$ W, which is similar to the simulated 19  $\mu$ W. The output power was 63  $\mu$ W, but the power consumption through the output stage was measured as 135  $\mu$ W (separated supply pad were included for the control loop and output stage), resulting in an efficiency of only 40 %. While the measured efficiency is still much better than using a linear regulator or powering the

Fig. 13 An SMU was used for biasing and to generate the input voltage, while measuring consumption. Both Vm and VOUT were measured using an oscilloscope

Fig. 14 Detail of the Vm voltage during the switching. The 200 ns delay of the ZCD circuit results in the decrease of efficiency

amplifier with the battery voltage (>19 % efficiency) it is still much lower than expected.

Since the missing energy is lost in the switches (the use of different power supplies for the different blocks, allowed the determination of the exact location of the extra power consumption), the problem is either the short-circuit current through the output MOSFETs, or the ZCD not working correctly.

Table 1 Simulated

characteristics

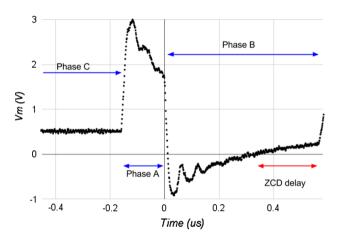

In Fig. 14, a detail of the measured voltage Vm during Phase A, Phase B and the beginning of Phase C is shown. As explained in section II, Phase B should end when the ZCD detects the change in Vm, but instead it is ending approximately 200 ns later.

In this 200 ns time slot, some amount of energy already delivered to the output capacitor is removed. The total energy wasted during this period was calculated, and results in an average power consumption of 56  $\mu$ W. If this loss was not present, total consumption through the output stage would be 79  $\mu$ W, and the efficiency would be  $\eta = 63$  %, much closer to the simulated results. This result confirms that the main efficiency problem is caused by a ZCD slow reaction to changes that was not detected during simulation (all corners and mismatch were examined during simulations). New methods for detecting the switching time are being considered for a second version of the circuit.

Table 1, displays a list of the simulated, and measured characteristics.

## 4 Conclusions

A DC/DC converter for micro-power applications was designed, fabricated in a 0.6 µm technology, and measured. The circuit fulfilled most of the initial requirements. It can operate from an input battery of 1.9 to 5 V, and can generate an output voltage from 0.2 to 1.5 V. Such a low output voltage may help to power very efficient analog and digital circuits without a significant battery current drain in the case of implantable electronics. The measured efficiency of the converter was 40 %, below the simulated 70 % average expected. The extensive measurements and analysis show that the zero-crossing detector that is part of the feedback loop is working slower than expected, being responsible of most of the extra energy loss. This work complements reported work in the field of micro-power converters. While the efficiency issue still has to be improved, the output voltage shown to be precise and stable in a wide range of operating conditions, particularly those with a large gap between the input and a low voltage output where some converters fail. Inductive DC/DC

| Characteristic           | Simulated (range) | Measured (only actually measured cases shown) |

|--------------------------|-------------------|-----------------------------------------------|

| Simulated input voltage  | 2.5–5.0 V         | 1.9 5.0 V                                     |

| Simulated output voltage | 0.3–1.5 V         | 0.2–1.5 V                                     |

| Output load              | 12–120 μW         | 55 and 160 µW                                 |

| Commutation frequency    | 15–40 kHz         | 19 kHz                                        |

| Voltage ripple           | <5 %              | <5 %                                          |

| Efficiency               | 60–75 %           | 40 %                                          |

converters show promissory as a way to efficiently reducing power consumption in implantable medical devices among other ultra low power applications. Inductive converters may reduce the component count of the power management system especially in the case of multiple output voltages, and unlike charge pumps have no major restrictions in the programmed output values.

# References

- Gak, J., Miguez, M., & Arnaud, A. (2008). "On the reduction of thermal and flicker noise in ENG signal recording amplifiers". *Journal Analog Integrated Circuits and Signal Processing*, 57(1–2), 39–48.

- Tangt, W. X., Tung,S., Wen,S.,Lin, K. (Jun 2013) "A 70 μW/ MHz ultra-low voltage microcontroller SPARK". *Proceedingss* of the 2013 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC) (pp. 1–2). IEEE.

- Srinivasa Sridhara, R., et al. (2011). Microwatt embedded processor platform for medical system-on-chip applications. *IEEE Journal of Solid-State Circuits*, 46(4), 721–730.

- TS3310, ultra low power boost converter, datasheet http://www. silabs.com/Support%20Documents/TechnicalDocs/TS3310.pdf.

- Wong, L. S. Y., et al. (2004). A very low power CMOS mixed signal IC for implantable pacemaker applications. *IEEE Journal* of Solid State Circuits, 39(12), 2446–2456.

- Gak, J., Arnaud, A., Miguez, M. (Feb 2013) "A programmable charge pump voltage converter for implantable medical devices in a HV technology". *Proceedings of the 2013 IEEE Fourth Latin American Symposium on Circuits and Systems* (LASCAS) (pp. 1–4). IEE.

- O. Al-Terkawi Hasib, M. Sawan and Y. Savaria, "A Low-Power Asynchronous Step-Down DC–DC Converter for Implantable Devices," in *IEEE Transactions on Biomedical Circuits and Systems*, vol. 5, no. 3, pp. 292-301, June 2011. doi: 10.1109/TBCAS.2010.2103073.

- George, L., Gargiulo, G. D., Lehmann, T., & Hamilton, T. J. (2016). A 0.04 mm Buck-boost DC–DC converter for biomedical implants using adaptive gain and discrete frequency scaling control. *IEEE Transactions on Biomedical Circuits and Systems*, *10*(3), 668–678. doi:10.1109/TBCAS.2015.2480035.

- TPS62736, TPS62740, ultra low power step down converters, datasheet http://www.ti.com.

- MSP430L09x, low voltage microcontroller, datasheet http:// www.ti.com.

- Chu, L. C., Yang, T. F., Huang, R. Y., Su, Y. P., Lin, C. H., Wey, C. L., .. & Tsai, T. Y. (2015, November). 200nA low quiescent current deep-standby mode in 28nm DC-DC buck converter for active implantable medical devices. In *Solid-State Circuits Conference (A-SSCC), 2015 IEEE Asian* (pp. 1–4). IEEE.

- Shi, L. F., & Jia, W. G. (2014). Mode-selectable high-efficiency low-quiescent-current synchronous buck DC–DC Converter. *IEEE Transactions on Industrial Electronics*, 61(5), 2278–2285. doi:10.1109/TIE.2013.2267697.

- Cheng, L., Liu, Y., & Ki, W. H. (2014, February). 4.4 A 10/30MHz Wide-duty-cycle-range buck converter with DDA-based Type-III compensator and fast reference-tracking responses for DVS applications. In 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) (pp. 84–85). IEEE.

- 14. Ang, S. S., Oliva, A. (2005) *Power-Switching Converters*. CRC press.

- Bengoechea, F., Aguirre, G., Gak, J. (Aug.2012)"10 BITS Analog-to-Digital Converter" *Proceedings*. Argentine CAMTA 2012—Cordoba, Argentina.

- Arnaud, A., & Rossi, C. (2001, March). Análisis de una cadena de inversores asimétricos como elemento de retardo. In VII Workshop de Iberchip, Montevideo.

- Miguez, M., Gak, J., Costa, G., & Arnaud, A. (2012, August). A low-voltage, low-power 1.03 V voltage reference for implantable medical devices. In *Micro-Nanoelectronics, Technology and Applications (EAMTA), 2012 Argentine School of* (pp. 47–51). IEEE.

- 18. Quallion Batteries, http://www.quallion.com/sub-sp-main.asp.

- 19. Taiyo-Yuden CBC3225T101KR, http://www.ty-top.com/.

Matías R. Miguez (M'06) received his M.Sc. and Graduate degree in Electronics Engineering from the Universidad Católica, Montevideo Uruguay in 2008 and 2005 respectively. He has also received a Graduate degree in Physics from the Universidad de la República, also in Montevideo, Uruguay in 2007. In 2005, he joined the Electrical Engineering Department, Universidad Católica, Montevideo, Uruguay. Since 2005 he has been involved in

research projects in the field of CMOS analog design and vehicular traffic modeling. He is a Doctoral Candidate in the Universidad Nacional del Sur, Bahia Blanca, Argentina.

Alfredo Arnaud received the M.S., and Ph.D. degree in electronics from the Universidad de la República, Montevideo-Uruguay, in 2000, and 2004. Since 1997, he was involved in several research and industrial projects, in the field of CMOS analog design, and optoelectronics. In 2004, he joined the Electrical Engineering Department, Universidad Católica, Montevideo-Uruguay.

Alejandro Raúl Oliva received the B.S.E.E. degree from the Universidad Nacional del Sur (UNS), Bahía Blanca, Argentina, in 1987, and the M.S. and Ph.D. degrees in electrical engineering from the University of Arkansas, Fayetteville, AR, USA, in 1996 and 2004, respectively. He has been a Professor in the Electrical Engineering Department of the UNS since 1999. He has been a member of the Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET), Buenos

Aires, Argentina, since 2005. He has published a book and more than

🖉 Springer

50 journals and proceedings. His main research interests are power electronics and power management.

Pedro Julián (S'93–M'99– SM'05) received the Electronic Engineer degree and the Ph.D. degree in control de sistemas from Universidad Nacional del Sur (UNS), Bahía Blanca, Argentina, in 1994 and 1999, respectively. He was a Visiting Scholar with the University of California Berkeley, Berkeley, CA, USA, from 2000 to 2002, Visiting Scholar from 2002 to 2003, and Visiting Fulbright Professor with Johns Hopkins

University, Baltimore, MD, USA,

in 2009. He was an Associate Professor with the Departamento de

Ingeniería Eléctrica y Computadoras, UNS, and as an Independent Researcher with the National Research Council of Argentina, Buenos Aires, Argentina. His current research interests include the theory and applications of computational circuits and systems, electronic systems, in particular sensory processors (acoustic and vision), with emphasis on low power VLSI systems. Prof. Julián served as the Region 9 (Latin America) Vice President and on the Board of Governors of the IEEE Circuits and Systems Society from 2004 to 2007, and he is a Founding Member of the Latin American Consortium for Integrated Services and the Argentine School of Microelectronics. He is a recipient of the Bernardo Houssay 2009 Prize of the Ministerio de Ciencia, Tecnología e Innovación Productiva and the 2009 Electronic Engineering Prize of Academia Nacional de Ciencias Exactas, Físicas y Naturales. He serves as an Associate Editor of the International Journal of Circuit Theory and Applications, the CASS Magazine, and the CASS Newsletter.